为了帮助日益壮大的设计队伍,EDA行业必须为设计人员提供能够使整个流程顺利执行的自动化解决方案。这些解决方案必须对功率进行优化,同时满足所有其它的设计和市场要求,包括速度、成本和IC制造良率。

功率问题概况

通过在系统级进行权衡取舍,作出相关决策,可以最大限度地降低消费设备的功率和能耗。有关系统划分 (亦即确定哪一种功能性由硬件还是软件来实现)、元件及IP选择的决策,对降低功率和系统性能及功能性的影响最大。

例如。在一个基于硬盘的MP3播放器中,对功率管理而言,关键的架构性特征之一是软件控制数据缓冲系统,其允许硬盘每次提供相当于长度几分钟的 音乐,然后停止旋转,等待下一次的音乐。尽管现在许多移动电话都已在架构级对语音通信进行了高度优化,来自消费者的压力仍然迫使设计师增加从电邮到流视 频,乃至MP3播放器的大量其它功能。

这样一来,系统设计师又不得不使用越来越激进的架构来管理功率。为了支持这种工作,EDA行业不断提高自身的系统级功率建模工具,以向系统设计人员提供关于其架构性决策的影响的反馈信息。

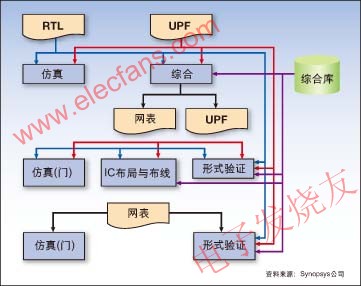

图:在设计中与golden RTL协作,通过DVFS和功率门控技术,在全设计流程中系统化地使用UPF来降低动态和静态功耗。

硬件功率管理技术

一旦确定了系统架构,选定了主要的应用IC,就可以运用各种硬件功率管理技术了。

RTL设计人员可以利用各种技术,如时钟门控、逻辑和单元电路级功率优化,以及多线程电压设计等,作为一个标准的基于综合的设计流程的一部分。 这些技术的自动应用可以降低功耗,同时保持性能、可测试性与可制造性。但这需要一个集成时钟门控单元和逻辑单元的库来提供多个驱动力度和多个阈值电平,还 需要工具来使用这些单元库的功能。现在的EDA工具就具有这类能力,而这些技术的使用也越来越普及。而更加激进的功率管理方法仍在设计原则和EDA工具能 力的前沿。

动态功率与V2成正比,故要把动态功率降至最小,关键在于降低电源电压。设计人员已开始采用片上多电压域:较高的电压域用于高性能模块,比如处 理器和缓存;较低的电压域用于其它工作频率较低的模块。该方案需要在工作电压不同的模块间插入电平转换器。这种大胆的设计是根据主要元件(比如处理器)的 工作负载,动态地为它们分配电源电压和时钟频率,被称为动态电压频率调变(DVFS)技术。

随着工艺几何尺寸不断缩小到90纳米、65纳米及以下,漏电流问题越来越突出,限制了手持设备的电池寿命。为了把泄漏功率降至最低,设计人员开 始采用功率门控技术—关断未在使用的模块的电源,通常是利用片上开关关断。这样,在那些断电和上电的域间就需要隔离单元,还需要一种策略来保 存关断期间的状态。

对于那些有峰值处理要求(如视频编码/解码)但又有大量时间处于空闲状态下的消费应用而言,这些技术极为有效。利用一种自适应功率管理方案,设计人员就可以最大限度地提高所设计芯片的性能,而当设计中某些模块的工作负载减少时使其以超低功率模式工作。

通过正确的硬件设计及其它因素,DVFS和功率门控技术可通过软件来控制,实现大幅度节能,延长电池寿命。

这些自适应技术都需要更加智能的设计自动化技术和更加灵活的IP。设计人员需要一种办法来详细说明功率意图,即明确哪一个域由哪一个电源供电, 哪一个域可被关断,以及什么时候采用什么策略来保存关断期间的状态。设计人员一般都希望这种设计意图的确定与RTL无关,因为特定的RTL模块在不同的应 用中可能有不同的功率意图。

因此,实现工具需要设置功率意图,并在适当的位置插入电平转换器、隔离单元和保持寄存器,并把功率正确路由到芯片中的所有器件。尤其是,这些工具需要对信号进行适当缓冲,亦即,当需要信号时缓冲器上电,不需要时关断。这些路由规则中有一部分可能会变得相当复杂。

签核工具现在必须包含电压依赖性时序和功率网格完整性。验证(规则的和动态的)必须能够处理因增加功率门控技术而产生的设计行为的变化。IP供 应商也必须协助开发出范围更广泛的低功率IP,包括电平转换器、隔离单元、保持触发器和功率门控开关。为了支持DVFS,还必须对单元库进行特性化以用于 大电压范围,而不仅仅局限在一两个特殊的工作点上。

统一功率格式

幸运的是,业界主流公司已开始联手协作推出低功率解决方案,把更加自动化的EDA工具、更灵活的IP、标准 格式和功耗要求更严格的工艺技术整合到真正的端到端解决方案中。最近,Accellera标准组织内有一大批领先的半导体、EDA和IP公司联盟正在积极 开发一种统一功率格式(UPF)。UPF提供了一个机制来描述与RTL无关设计的功率意图。它允许设计人员定义功率门控所需的功率域、隔离策略和保持策 略。它还允许设计人员定义电平转换器策略和功率状态表,用来处理多个功率域。利用UPF,可以使全设计流程中的所有工具统一化,以实现和验证同一套功率降 低策略。

在设计中与golden RTL协作,通过DVFS和功率门控技术,在全设计流程中系统化地使用UPF来降低动态和静态功率。