文献标识码: A

文章编号: 0258-7998(2015)03-0044-04

0 引言

由于基于ΣΔ调制技术的ΣΔ模数转换器(ADC)易于与数字芯片集成,并且对于器件的失配不是很敏感,所以是目前高性能无线通信和传感器微弱信号检测电路的首选[1]。采用过采样技术和噪声整形技术的调制器是限制ΣΔ ADC性能的关键模块,所以设计高性能的ΣΔ调制器是实现高精度的ΣΔ ADC的必经途径。目前关于ΣΔ调制器的研究主要集中于两阶~四阶结构,这是由于高阶的调制器面临稳定性问题。在设计低阶的调制器时可以通过提高过采样率来部分提高性能[2-3]。然而提高系统过采样率会提高对运放带宽的要求,增加系统的功耗。在消费电子领域,对于芯片的功耗有一定的限制,所以在较低的功耗下设计一种高性能的调制器很有意义。本文的目标是在较低的功耗下设计出一种适用于加速度传感器的高性能ΣΔ调制器电路。通过参数优化和建模仿真,在较低的采样频率下实现一种五阶单环一位结构的ΣΔ调制器电路。利用根轨迹法分析和验证该高阶系统的稳定性,通过版图后仿真结果显示提出的五阶结构实现了较高的性能,满足系统设计要求。

1 系统设计

图1是设计的五阶ΣΔ调制器原理框图,该调制器采用前馈单环一位结构,该结构能够减小积分器的输出摆幅,降低对运放的性能和设计指标要求,提高了系统的线性度。同时采用前馈结构使得积分器输出摆幅大大减小,能够降低系统的功耗,有利于低功耗的设计目标。表1是经过优化的调制器的各级系数,包括前馈系数和各个积分器的增益因子。

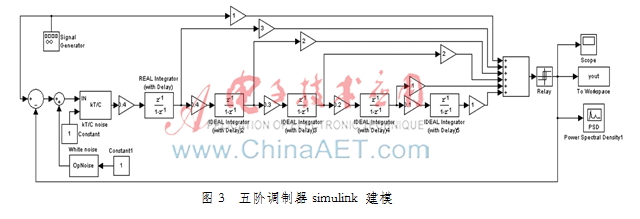

虽然提高阶数能够提高系统的性能,但是高阶系统存在严重的稳定性问题。为了验证系统的稳定性,可以在MATLAB中求解噪声传递函数的根轨迹曲线来判断系统的稳定性,结果如图2所示。仿真结果显示该高阶系统是条件稳定的,当量化器的增益小于0.525时,极点进入单位圆外,系统出现稳定性问题,所以量化器的输入存在一个稳定范围,也即调制器的输入信号不能太大,否则会导致系统不稳定。在MATLAB中搭建该五阶调制器的行为级模型,如图3所示。其中包含运放热噪声和第一级积分器的kT/C噪声模型,而且在第一级积分器模型中引入了有限增益带宽等非理想因素,以便更真实地模拟实际调制器电路的仿真结果。由于加速度计传感器的应用频带较低,一般在几百赫兹以内,所以在过采样率为125的情况下,图3中的调制器的采样频率可以大大降低。在输入信号幅度为-1.94 dBFS,信号频率488.24 Hz,采样频率为250 kHz的条件下,图3中的65 536点输出位流频谱如图4所示,实现了大于18位的精度,满足了加速度计接口电路中关于后级高精调制器的带宽和精度要求。

2 电路实现和版图后仿

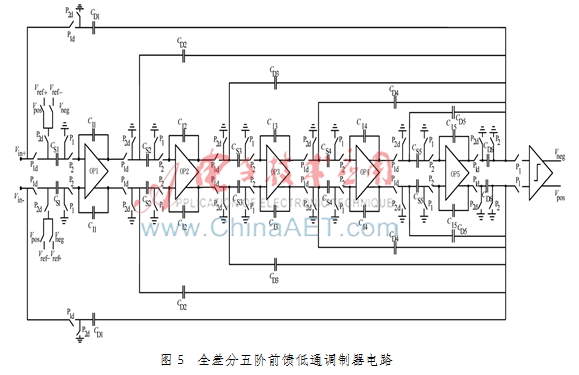

本设计的五阶低通ΣΔ调制器电路采用开关电容电路实现,如图5所示。在设计时采用全差分结构来消除电路的偶次谐波分量,从而提高整体电路的性能。整体电路由五级积分器电路、前馈求和电路以及动态锁存比较器等组成,并由控制时序P1、P1d、P2、P2d控制开关的开启和关断。其中P1d和P2d分别是P1、P2的延迟时序,这样设计的目的是减小开关关断时的电荷注入引起的噪声[4]。由于采用了高阶调制结构,后级积分器的噪声可以经过前级整形,所以第一级积分器决定着整体的性能,后级积分器的带宽和增益等参数可以适当降低[5]。前馈求和电路采用简单的无源开关电容电路,减小芯片面积和功耗。求和电路在P1相求和,比较器对输入差分信号比较输出;求和电路在P2相复位,比较器输出锁存。本设计的量化范围Vpp=1.65 V,分辨率为N=18,OSR=125。根据建模仿真结果选取CS1=4 pF,第一级积分器的运放积分电容为10 pF。由于后级电路的噪声可以通过前级抑制,后级积分器电路的采样电容可以大大减小,故积分器的负载电容也等比例减小。

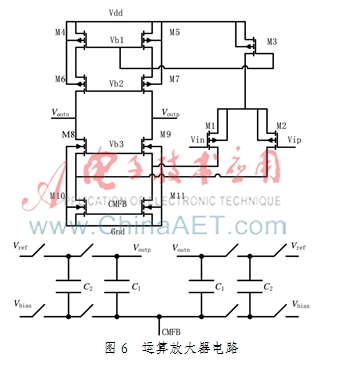

运放的有限增益会改变积分器的极点位置,产生积分泄露,也就改变了系统的噪声传递函数的极点。通过行为级仿真扫描可以确定运放的直流增益需大于60 dB才能保证系统的精度。为了简化设计,选择一级折叠共源共栅放大器来实现积分器电路,运放的电路图如图6所示。在第一级积分器负载电容为10 pF时,仿真得到的运放电路直流增益为78 dB,单位增益带宽约为12 MHz,相位裕度为66°,摆率为15.7 V/μs,功耗约为1.4 mW。后级积分器的负载电容等比例缩放,对运放的增益和带宽要求也大大降低,因此可以降低功耗。后级4个运放在负载电容等比例缩小的情况下总体功耗小于1.5 mW。由于采用了一位量化,所以用比较器来实现调制器电容中的一位量化器,实现输出数字信号。动态比较器具有电路简单、速度较快、功耗低的特点。

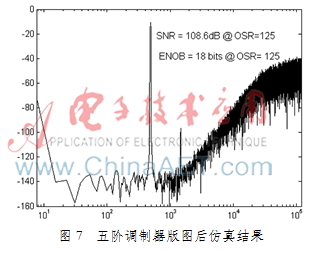

设计的五阶低通ΣΔ调制器电路采用CHRT 0.35 μm CMOS工艺实现,系统工作在3.3 V的电源电压下。通过提取出版图寄生参数,在Spectre下进行后仿验证,输入信号幅度为500 mV的差分正弦信号,信号频率488.28 Hz,系统的采样频率为250 kHz。将瞬态仿真的位流导出到MATLAB下进行频率分析,65 536点的FFT结果如图7所示。系统的信噪比达到108.6 dB,有效位数约为18位,总体功耗3.4 mW。由于开关和运放的非线性以及版图的对称性问题导致图7中出现了3次谐波失真。

3 结束语

本文在CHRT 0.35 μm CMOS工艺下实现了一种用于加速度计信号检测的高精度ΣΔ调制器。后仿真结果表明在1 kHz的信号带宽内,实现了约18位的有效位数,整体功耗只有3.4 mW。通过后仿真结果和行为级建模的结果对比可以证明设计的五阶单环调制器电路实现了设计目标,达到了性能要求。

参考文献

[1] 范军,黑勇,陈铖颖.一种采用斩波——稳零技术的低功耗Σ-Δ调制器的设计[J].微电子学与计算机,2011,28(11):76-80.

[2] 刘燕娟,程东方.用于电池电量测量的Delta-Sigma调制器设计[J].微电子学与计算机,2013,30(7):82-85.

[3] Chen Hsinliang,Chen Po-sheng,Chiang Jen-shiun.A low-offset low-noise sigma-delta modulator with pseudorandom chopper-stabilization techniques[J].IEEE Transactions on circuits and systems-I:Regular Papers,2009,56(12):2533-2543.

[4] LEE K L,MEYER R G.Low-distortion switched-capacitor filter design techniques[J].IEEE Journal of Solid-State Circuits,1985,SC-20(6):1103-1112.

[5] 张永来.18位精度音频Sigma-Delta ADC的设计[D].哈尔滨:哈尔滨工业大学,2013.