马赵,任尚坤,杨梅芳

(南昌航空大学 无损检测技术教育部重点实验室,江西 南昌 330063)

摘要:激励信号源是电磁超声检测系统的核心模块之一,其输出信号决定了电磁超声检测仪检测的质量。按照电磁超声检测系统对激励源的要求,设计了相应的正弦脉冲激励源。该设计系统主要包括FPGA的硬件语言合成脉冲信号、D/A转换、滤波放大、功率放大和阻抗匹配等硬件电路。该系统可输出频率、初始相位、占空比可调的脉冲正弦信号,满足EMAT对激励源的要求。可为设计便携式的电磁超声检测仪提供借鉴。

关键词:FPGA;电磁超声检测;信号源;硬件电路

中图分类号:TG115.28文献标识码:ADOI: 10.19358/j.issn.16747720.2016.23.024

引用格式:马赵,任尚坤,杨梅芳. 基于FPGA的电磁超声脉冲信号发生器的设计[J].微型机与应用,2016,35(23):83-85,89.

0引言

电磁超声检测技术(EMAT)是一种新兴的无损检测技术,与传统的压电式超声检测技术相比具有明显的优势。其具有无需耦合剂、非接触性、能够在高温高压等特殊环境中正常工作等优点,将具有极大的潜在市场价值和广阔的发展前景[1]。

电磁超声检测系统主要由激励源、EMAT传感器、接收信号处理系统3部分组成。EMAT传感器由激励探头和接收探头组成[1]。电磁超声检测原理可以概括为:高频线圈中通过高频高压强电流的激励脉冲信号,在外部偏置磁场作用下,在被测工件的表面或内部产生不同的超声波。其接收过程与激发过程互为逆过程,接收系统对探头接收到的回波信号进行处理,输出到信号显示端[2]。可以通过对有缺陷的回波信号和无缺陷的回波信号进行观察分析,来确定缺陷的位置和大小。

目前而言,EMAT还处于研发阶段,激励源的换能效率比较低,导致激发出的超声波的信噪比较低。高质量的激励信号源是提高检测效果的重要保证,本研究的目的是设计制造出高效可靠的电磁超声激励源系统[3]。

经过查阅大量相关资料得到,通常采用PWM技术设计脉冲式信号发生器,但该方法输出激励信号存在易失真、谐波大、初始相位不稳定等不足。本设计主要采用FPGA技术合成正弦脉冲信号,设计出可靠的脉冲信号发生器。

1硬件电路设计

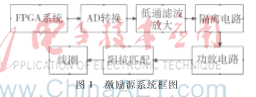

整个硬件系统主要包括FPGA系统、AD转换电路、低通滤波放大电路、隔离电路、功放电路、阻抗匹配电路等[4],其系统框图如图1所示。

(1)FPGA系统

本设计采用了Altera公司的cyclone II系列的EP2C8Q208C7可编程器件。该可编程器件功能强大,I/O端口丰富,输入时钟频率理论上能达到200 MHz。本设计采用输入时钟为50 MHz的有源晶振提供系统时钟信号。另外通过PLL程序设计,提高输出数字信号的频率,使之能够达几百千赫兹到几兆赫兹,完全能够合成满足条件的脉冲正弦信号。

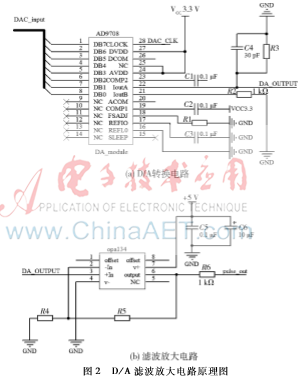

(2)D/A滤波放大电路的设计

在提高FPGA高速输出数字信号的同时,也需要采用高采样速度的并行D/A芯片。本设计采用ADI公司的AD9708芯片,它是一种8 bit高速D/A转换芯片,其最高采样速度能达到125MS/s,能够将FPGA并行发出的数字信号转化为相对应的模拟量。

FPGA 输出的数字信号经过D/A芯片的转换,输出模拟信号,通过低通滤波放大电路进行滤波放大。低通滤波放大电路主要由无源电容电阻并联滤波电路和放大芯片电路组成,放大芯片采用了OPA134运算放大芯片对滤波后的信号进行运算放大。其设计原理图如图2所示。

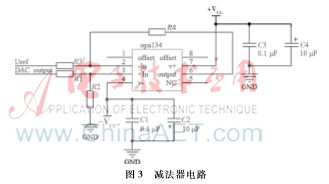

经过运算放大芯片,输出脉冲正弦信号只有正向电压。脉冲信号通过减法器电路输出交流电压。减法器(Subtracter)同样采用TI公司的OPA134运算放大芯片,其电路原理图如图3所示。

(3)信号功率放大电路设计

EMAT要求输出的激励脉冲功率大,需要输出的脉冲功率达到几百瓦甚至是几千瓦。越高的激励功率越容易在检测工件内部激励出超声波。考虑到输出信号的功率大,将输出的脉冲信号先通过1:1的绕线比例变压器将脉冲发生电路与功放电路进行隔离,从而减小后期的功率放大对信号发生电路产生的影响[3]。

设计采用了集成功放芯片对合成的脉冲信号进行功率放大。采用的集成功放芯片是TDA7293功率放大芯片,能够有100 W的输出功率。同时为了使线圈获得最大的功率,需要对电路进行阻抗匹配设计。

(4)阻抗匹配电路设计

阻抗匹配电路是电磁超声检测系统的重要组成部分,阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出。对于不同特性的电路,匹配条件是不一样的。对于纯电阻而言,电源内阻的大小等于外部电阻的大小,此时外部负载能够获得最大的功率;对于阻抗电路而言,其输入阻抗与输出阻抗共轭,此时负载能够获得最大的功率[3]。

2FPGA激励源数字系统设计

现场可编程门阵列(FPGA)是一种采用硬件编程语言编程的器件,具有灵活的、可编程的逻辑门阵列芯片。利用硬件描述语言(HDL)能够完成各种数字电路系统的设计,减少了传统逻辑门芯片的数量,简化了硬件电路设计;FPGA器件的时钟频率能达到几十兆甚至几百兆赫兹,完全能够满足合成高频信号的要求 [5]。

本文主要利用FPGA器件合成所需要的脉冲式正弦信号。由于EMAT需要的激励信号是脉冲式的,若直接采用DDS芯片作为激励输出信号,其输出的信号是连续的,很难通过硬件控制或者软件编程,使其输出的信号呈现脉冲周期性;同样采用高速开关控制,很难保证信号的周期性。经过多方面考虑,采用FPGA器件,利用硬件编程语言合成脉冲信号。FPGA合成脉冲正弦信号包括两部分,即 FPGA查找表的设计和Verilog HDL语言编程实现输出。

2.1FPGA查找表的设计

查找表(LUT)是合成波形的关键部分,如何建立查找表至关重要。本设计采用MATLAB软件工具,编程产生一个周期的正弦波形,并采样正弦图像若干个点,提取出相应的点所对应的数值。经过一系列的数字处理,将处理后的数值输入到quartus II 新建的rom文件中。具体设计如下:

(1)设置正弦波的相关参数。在MATLAB中设置正弦函数的频率、初始相位、采样频率、采样点数、振幅以及直流分量的值,使MATLAB能够输出一个周期的正弦波形。本设计如下:

f=1;Fs=256;P1=0;

N=256;t=[0:1/Fs:N/Fs];

A0=128;A=128;

s=A*sin(2*pi*f*t + pi*P1/180) + A0;

B=round(s);plot(s);

其中f为信号频率,本设计只需输出一个周期的波形,即f=1;Fs为采样频率,满足Fs>2f;N为采样点数;s为函数表达式;B中的值是s四舍五入后的值。

(2)在MATLAB的workspace对话框中提取B的值,输入到quartusII新建的Memory Initialization File文件中,建立sin.mif文件。其数据格式如图4所示。

2.2FPGA编程合成信号

现场可编程门阵列(Field Programmable Gate Array,FPGA)是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的。Verilog HDL 硬件描述语言广泛应用于数字系统设计中,本设计也采用了该硬件描述语言来描述FPGA内部数字系统的设计,从而输出满足要求的脉冲信号 [2]。

本设计的核心思想是对Look-up Table读取地址所对应的数据,通过时钟控制输入到D/A芯片的数字端口,转换成模拟信号。首先在设计模块中定义出相关的输入输出端口,输入输出端口主要包括时钟输入端CLK、复位输入端口RST_B、8位数据输出端q端口、输出DAC芯片时钟信号端口。模块设计端口设置如下:

/***********I/O Port*************/

input CLK;

input RST_B;

outputq;

outputDAC_CLK ;

wireCLK;

wireRST_B;

wire[7:0] q;

wireDAC_CLK;

ROM例化到模块电路中代码:

/**********ROMinstance************/

ROM_P I_ROM_P(

. address (addr),

.clock (CLK),

.q(q ));

例化后的mif文件导入到数字模块中,程序模块生成数据地址,将地址匹配到ROM_P的地址,从而读取地址所对应的数值。在硬件层面,通过时钟信号的控制,将ROM_P中地址对应的数值送到D/A芯片的输入端,从而转化成模拟信号,合成所需要的正弦脉冲信号。

3实验结果

在完成相关设计后,对硬件电路和FPGA数字系统进行相关调试,完成相关的测试。设置相关的参数,利用quartusII软件平台,将设计的数字系统下载到硬件系统中。

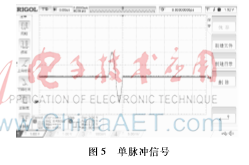

用数字示波器显示出单通道正弦脉冲信号的波形,如图5和6所示。通过FPGA控制调节设置相应的参数, 输出多脉冲信号波形,如图7所示。

本设计可以产生可控周期数的正弦脉冲信号,且其脉冲信号的频率可以通过设置相应的参数来调节,调节范围可达几十千赫兹至几兆赫兹,完全能够满足电磁超声脉冲信号发生器的要求。

4结论

信号发生器是电磁超声检测系统的核心组成部分之一,本文设计的脉冲式正弦信号发生器能够提供较为稳定的正弦脉冲信号。研究结论如下:

(1)采用FPGA芯片,利用硬件编程语言合成脉冲信号,具有频率高、信号稳定的特点,克服了直接采用DDS芯片作为激励输出信号连续性的不足,使输出的信号由连续式变为脉冲式,并且简化了模块电路的设计。

(2)利用FPGA芯片产生脉冲式正弦信号,能够精确控制高频脉冲信号输出,通过功率放大隔离和阻抗匹配,能够产生适合电磁超声检测的激励信号。该设计克服了采用PWM传统技术输出信号易失真、谐波大、初始相位不确定等不足。

参考文献

[1] 黄松岭,王坤,赵伟. 电磁超声导波理论与研究[M]. 北京:清华大学出版社,2013.

[2] 潘伟才. 基于FPGA的电磁超声检测系统的研究[D].哈尔滨:哈尔滨工业大学,2008.

[3] MIRKHANI K, CHAGGARES C,MASTERSON C,et al. Optimal design of EMAT transmitters[J]. NDT & E International, 2004, 37(3): 181-193.

[4] 金哲.钢轨应力的电磁超声检测技术研究[D].南京:南京航空航天大学,2011.

[5] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008.