3nm、5nm关键技术:国内专家搞定GAA晶体管

2020-12-19

来源:快科技

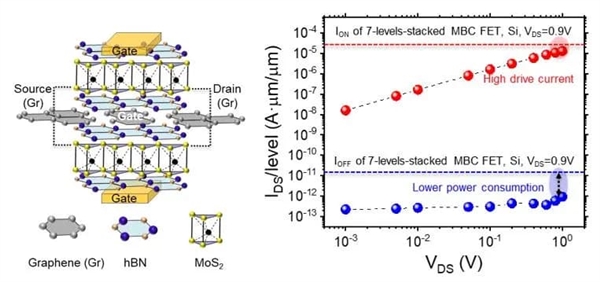

来自复旦大学微电子学院的消息,该校周鹏团队针对具有重大需求的3-5纳米节点晶体管技术,验证了双层沟道厚度分别为0.6 /1.2纳米的围栅多桥沟道晶体管(GAA,Gate All Around),实现了高驱动电流和低泄漏电流的融合统一,为高性能低功耗电子器件的发展提供了新的技术途径。

据悉,相关成果已经在第66届IEDM国际电子器件大会上在线发表。

报道提到,工艺制程提升到5nm节点以下后,传统晶体管微缩提升性能难以为继,需要做重大革新。于是GAA晶体管乘势而起,它可实现更好的栅控能力和漏电控制。

此番周鹏团队设计并制备出超薄围栅双桥沟道晶体管,驱动电流与普通MoS2晶体管相比提升超过400%,室温下可达到理想的亚阈值摆幅(60mV/dec),漏电流降低了两个数量级。

据悉,GAA晶体管也被译作“环绕栅极晶体管”,取代的是华人教授胡正明团队研制的FinFET(鳍式场效应晶体管)。按照目前掌握的资料,三星打算从2022年投产的第一代3nm就引入GAA晶体管,台积电略保守,3nm仍是FinFET,2nm开始启用GAA。

另外,中芯国际梁孟松日前也披露,该公司的5nm和3nm的最关键、也是最艰巨的8大项技术也已经有序展开, 只待EUV光刻机的到来,就可以进入全面开发阶段。

双桥沟道晶体管示意图及其性能图

本站内容除特别声明的原创文章之外,转载内容只为传递更多信息,并不代表本网站赞同其观点。转载的所有的文章、图片、音/视频文件等资料的版权归版权所有权人所有。本站采用的非本站原创文章及图片等内容无法一一联系确认版权者。如涉及作品内容、版权和其它问题,请及时通过电子邮件或电话通知我们,以便迅速采取适当措施,避免给双方造成不必要的经济损失。联系电话:010-82306118;邮箱:aet@chinaaet.com。