SK海力士HBM4E被曝拟引入台积电3nm工艺

2026-03-23

来源:IT之家

3 月 22 日消息,据韩媒《朝鲜日报》,SK 海力士正考虑在其 HBM4E 中为承担核心处理功能的“逻辑芯片”引入台积电 3nm 工艺,从而进一步获取性能优势。

业内消息人士 3 月 20 日透露,SK 海力士计划在 HBM4E 的“核心芯片”(即堆叠的 DRAM)上使用 10nm 级第 6 代(1c)DRAM 工艺,而逻辑芯片则采用台积电的 3nm 工艺。

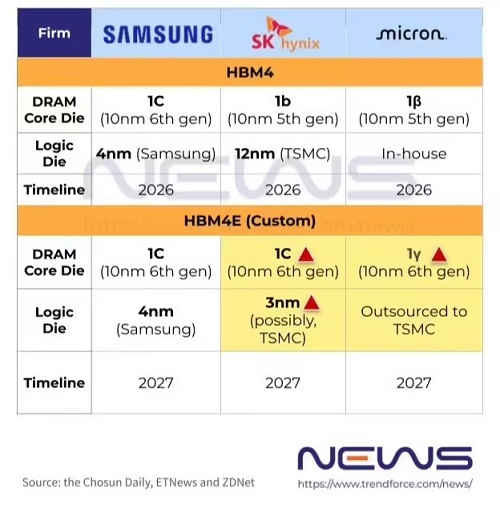

相比之下,今年 SK 海力士向英伟达供应的 HBM4 采用了 10nm 级第 5 代(1b)DRAM 核心芯片,逻辑芯片则使用台积电 12nm 工艺;而三星电子的 HBM4 则采用了 10nm 级第 6 代(1c)DRAM 工艺的核心芯片及 4nm 的逻辑芯片。

尽管 SK 海力士是目前英伟达最大的 HBM4 供应商,但据称其在性能评估方面却收到了落后于三星的评价。如IT之家前文所述,三星在 HBM4 上应用了比 SK 海力士更先进的工艺,所以性能领先也在情理之中。

SK 海力士此番在 HBM4E 的逻辑芯片上引入 3nm 工艺,显然是意在扭转这一局面。如果说 HBM4 更侧重于通过成熟工艺保障稳定性,那么 HBM4E 则旨在实现性能领先,确立技术优势。

▲ 图源:trendforce

报道指出,随着可根据客户需求定制逻辑芯片的“定制化 HBM”市场从 HBM4E 开始逐渐扩大,各类晶圆代工工艺都有可能被采用。HBM4E 将应用于英伟达下一代 AI 芯片的顶级版本“Vera Rubin Ultra”。SK 海力士计划向英伟达等主要客户供应性能最高的产品。

一位半导体行业内部人士表示:“对于定制化 HBM4E,逻辑芯片是根据客户规格制造的,因此 3nm 和 12nm 等工艺都在考虑之中。但预计 3nm 工艺将是供应给市场的大部分 HBM4E 逻辑芯片的主要选择。”

与此同时,AMD 和谷歌也已宣布计划在各自的下一代 AI 芯片中采用 HBM4E,竞争日趋激烈。另一位业内人士指出:“三星通过在英伟达年度 GTC 2026 开发者大会上展示 HBM4E,表明了其抢占下一代市场的意图。SK 海力士似乎在谋划要在下一代 HBM 的性能上也占据主导地位。”