1 前言

在任何一个高速高分辨率的模数转换器中,高精度和快速比较器总是起着至关重要的作用。与其它种类的ADC 相比,流水线ADC 有着高速、高分辨率的特点。因此,它在电子系统中,有着广泛的应用。流水线ADC由许多子FLASHADC 构成。流水线ADC 的特性中,特别是速度,功耗和失调电压对整个电路有着很重要的影响。适合流水线的动态比较器主要有三种:电阻分压比较器、差分比较器和电容差分比较器[1]。但是他们可能消耗过多的功耗和较大的失调电压。因此,前置运放锁存比较器的优势体现在3.5 位的子FLASHADC 或者更高分辨率的子FLASHADC 中。在考虑上面提及的因素后,本文给出了时间延迟、失调电压和比较器的踢回噪声的理论分析,并根据此分析,设计和优化了比较器电路。

2 预放大锁存比较器的工作原理

前置增益运放锁存比较器的原理是前置增益运放放大输入信号,被放大后的信号输入到锁存比较器,最后信号通过一个普通的RS 触发器,得到最终比较结果。这种结构结合了前置增益运放对输入信号负指数响应和锁存比较器对输入信号正指数响应的优点。因此前置增益运放锁存比较器与其它锁存比较器相比,有较小的传输的延迟。锁存比较器的失调电压除以预放大器的增益后折算到运放的输入端。因此,前置增益运放比较器的失调电压主要来自于预放大器。通过前置增益运放比较器输入端的踢回噪声,在信号的比较阶段混淆了输入信号。没有隔离电路可能导致采样电路的不稳定性和不精确的比较结果。因此在锁存比较器输入端和前置增益运放的输出端在之间需要一个隔离电路[2]。

3 电路的结构

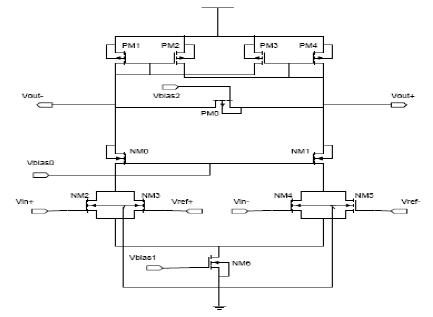

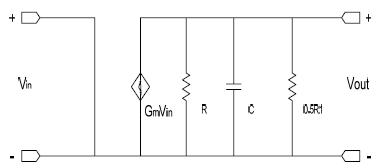

图1 给出了前置增益运放锁存器的电路结构。前置增益运放有两个差分对,分别由NM2,NM3,NM4 和NM5 组成。PM1,PM2,PM3,PM4 交叉相连形成一个正反馈回路,并且增大了前置放大器的增益。NM9,NM10,NM11,PM6,PM11 是开关。电路的工作流程为:当Clk 为低的时候,锁存比较器被复位,与此同时,Clk1 为高,锁存比较器能够接收到前置增益运放的放大的信号。加载在NM2 和NM3 栅上的差分输入信号,分别NM4 与NM5 栅上正相基准电平和负相基准电平相比较。两端各自产生的差分电流,流过共栅级后,差分负载迫使它流过接在输出两端的电阻R1,产生一个电压差(Vout+—Vout-),送到锁存比较器的输入端。当Clk 为高电平是,锁存比较器开始工作,差值(Vout+—Vout-)被交错连接的正反馈回路放大,直至稳定,一直到低电平的Clk 的到来。

(a) 前置增益运放

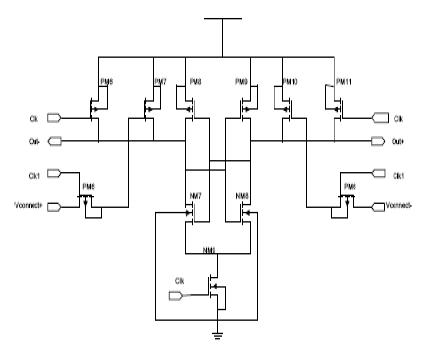

(b) 锁存比较器

图1 前置增益锁存比较器

3.1 前置增益运放锁存比较器的失调电压

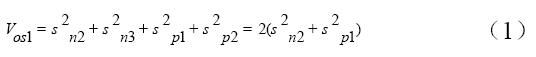

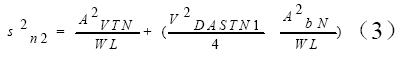

前置增益运放锁存比较器结构由带正反馈的前置增益运放和锁存比较器组成,所以比较器的失调电压主要由前置增益运放和锁存比较器的失调电压组成。前置运放放大了的差分信号用来出发锁存比较器,并且电路的正反馈提高了比较器的速度,增益也提高了。前置运放的失调电压Vos1 主要是由于NM2,NM3,NM4 和NM5 的不匹配造成的。根据文献[3]的分析方法,可以得到这样的式子[3][4],

公式(1)中,

,

,

而Vos2 主要由PM7,PM8,PM9,PM10 失配以及PM6 与PM12 关断引入的失配引起的电荷Q 所组成的,表达式为,

因此,总体的失调电压为,

根据公式(5),只要Av 足够的大,那么整个比较器的运放的失调就可以认为主要由前置增益运放的失调电压Vos1 造成的。

在公式(1)~(5)中,Avtn, Avtp, n Ab , 和p Ab 是与工艺相关的常数, 和

和 是前置运放负载晶体管的失调电压,

是前置运放负载晶体管的失调电压,![]() 和

和![]() 是输入晶体管的失调电压,因此加大晶体管的面积可以得到较小的失调电压。但是,这种方法将加大版图的面积以及寄生电容,而且也会降低比较器的速度。其实不用增大所有管子的面积,就可以减小比较器的失调电压。根据公式(5),可以增大增益Av 来减小Vos2 对比较器的失调影响。根据公式(1),可采用减小Vos1的方法如下:1)增大Av,用来减小NM2 和NM3 的失配对Vos1 的影响;2)适量的增加NM2 和NM3 的面积,以减小阈值电压的失配对Vos1 的影响。

是输入晶体管的失调电压,因此加大晶体管的面积可以得到较小的失调电压。但是,这种方法将加大版图的面积以及寄生电容,而且也会降低比较器的速度。其实不用增大所有管子的面积,就可以减小比较器的失调电压。根据公式(5),可以增大增益Av 来减小Vos2 对比较器的失调影响。根据公式(1),可采用减小Vos1的方法如下:1)增大Av,用来减小NM2 和NM3 的失配对Vos1 的影响;2)适量的增加NM2 和NM3 的面积,以减小阈值电压的失配对Vos1 的影响。

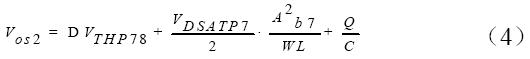

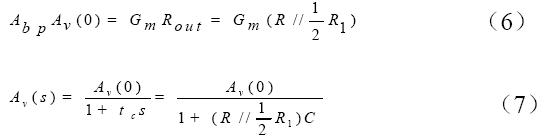

图2 为比较器的版图。版图的左边为前置运放的版图,右边为锁存比较器的版图。为了减小由于版图的失配带来的比较器的输入电压,前置运放和锁存比较器分别采用对称结构,增加比较器的对称性。

图2 比较器的版图

3.2 踢回噪声

在前置运放的输出端和锁存比较器的输入端之间需要一个隔离电路来减小踢回噪声[2]。在锁存比较器的两个输入端的晶体管的前面,分别加上一个PMOS管(PM6,PM11)作为开关管,晶体管的共栅电压用来控制信号。因此,踢回噪声对整个前置增益运放锁存比较器的影响就显著的减小了。

3.3 传输延迟时间的改善

有两种方法减小传输比较器的延迟:1)降低前置增益运放的时间常数;2)加大前置增益运放的A(s)[5][6]。

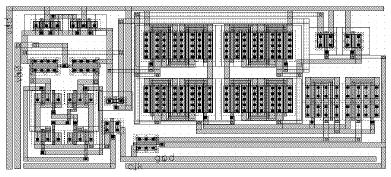

图3 为前置增益运放的交流小信号等效模型。根据图3,可得到等式(6),(7)

图3 前置增益运放的小信号等效模型

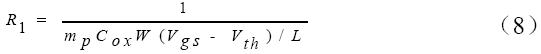

在上面的式子中,Av(0)为前置增益运放的直流小信号增益,Rout 是运放的等效输出阻抗, c t 为时间常数。R1 可以通过工作在深线性区的PMOS 管来代替,表达式为,

根据公式(6)(7),减小R1 可以使得 c t 减少,从而使响应速度指数增加,但是,同时减小R1,也使得Av(0)变小,从而使得响应速度线性下降。由此可见,与Av(0)相比, c t 对延迟时间的影响要显著多。因此,在设计时,对Av(0)要有个合理的设置。

4 模拟仿真与结果分析

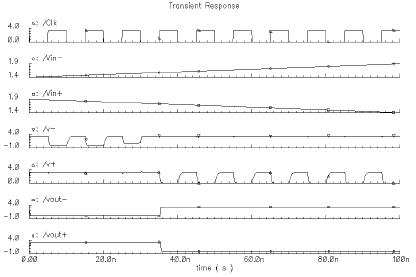

在Cadence Composer 环境,使用Spectre 对本文的比较器进行仿真。时钟的模拟频率为100MHz,电源电压为3.3v,模拟的条件为Typical。

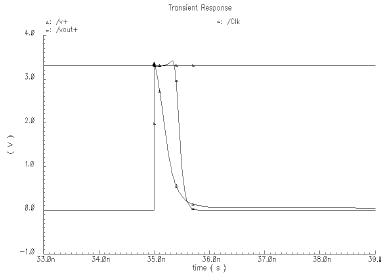

在图4 中,Vin+和Vin-为差分三角波信号,频率为2.5MHz,峰-峰值为1.455v~1.855v。Vref+和Vref-为差分直流信号,它们的差值为31.25mv,4 位子FlashADC 的1/2LSB。信号的共模电压为1.65v。V+和V-分别为锁存比较器的正负端输出,Vout+和Vout-分别为最终输出的正端和负端。从图4可以看出当Vin+和Vin-的差值小于1/2LSB 时,Vout+和Vout-的电压值发生翻转。图5为图4的局部放大图,可以看出传输比较器的延迟为680ps。在这种情况下整个电路消耗0.29mw 的功耗。

图4 比较器的仿真波形

图5 图4的局部放大图

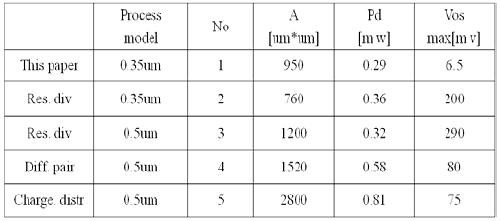

表1 中,前置增益动态比较器,电阻分配比较器(0.35um 和0.5um)、差分对比较器和电荷分配型比较器的性能进行总结。从表1中,可以看出与其它比较器相比,前置增益运放动态比较器拥有最低的功耗和失调电压。

表1 五种比较器的性能[1]

5 结论

本文介绍了一种高速电压比较器,采用了前置增益运放锁存比较器。根据仿真结果,比较器在100MHz 的采样频率下消耗0.29mw 的功耗,并且具有6.5mv的低失调电压。因此,此比较器较适合用于流水线ADC。

本文作者的创新点:采用前置增益运放锁存的结构并结合版图,减小了失调电压;增加了隔离电路,减小了踢回噪声;分析了前置增益运放,改善了传输延迟时间。

参考文献:

[1] Sumanen L, WaltariM, Hakkarainen V. CMOS dynamic comparators for pipeline A/D converters[A].IEEE Int Circ and Syst Symp[C].2002.Vol.5:157-160.

[2] Figueiredo P M,Vital J C.Low kickback noise techniques for CMOS latched comparators[A].IEEE Int Circ and Syst Symp[C].Vancouver Canada.2004.I-537-540.

[3] Gray P R,Hurst P J.Analysis and design of analog integrated circuits FM].New York:John Wiley& Sons,Inc.2001.

[4] Pelgrom MJM,Duinmaijer ACJ,Welbers APG,et al.Matching properties of MOS transistors.IEEE J Solid-State Circuits,1989,24(5):1433

[5] KY Kim, N. Kusayanagi, and A Abidi, A 10-b 100-MS/s CMOS A/D Converter, IEEE Journal of Solid-State Circuits, 32(3), 1998, 302-311.

[6] 刘涛,杨文荣,冉峰,王坤,邓霜。一种高速高分辨率C M O S比较器[z],微计算机信息,2006,04:209-211