基于AD9951的差分快速跳频系统频率合成器的设计

2008-07-29

作者:朱方明,张 辉

摘 要: 选用内部时钟为400MHz的高性能直接数字合成频率源DDS芯片AD9951作为核心器件设计频率合成器" title="频率合成器">频率合成器,采用DDS+DSP的设计方案。利用锁相环ADF4113为AD9951提供参考时钟。阐述了AD9951芯片的主要性能及其在快速频率合成器设计中的应用方法。

关键词: AD9951芯片;直接数字合成频率源;频率控制字

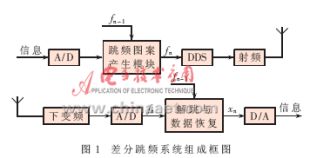

短波通信因其技术成熟、通信距离远、体积小、不易摧毁的特点,几十年来一直是实现远程通信和战术通信的主要手段,如何保证短波电台在敌方干扰下通信可靠有效,成为一个重要的研究课题。由于近十年来在数字信号处理技术(DSP)、超大规模集成电路和软件方面的新技术、新成果不断涌现,使得现代通信技术及短波通信技术得到飞速发展,尤其是跳频" title="跳频">跳频技术在短波通信中得到越来越重要的应用。差分" title="差分">差分跳频技术是一种新型的跳频通信技术,它利用跳变载波之间的相关性来传送信息。差分跳频技术应用于短波通信,可以在短波波段内实现宽频带、高速率的跳频,极大地提高了短波通信的数据速率及抗干扰、抗多径衰落能力,这种新型短波跳频系统将成为短波通信领域今后发展方向之一。图1是典型的差分跳频系统的组成框图。本文将针对短波差分跳频系统的特点,利用AD9951作为核心器件设计出适合于该系统的快速DDS频率合成器。

1 快速频率合成器特点及指标要求

短波差分快速跳频系统跳频速度达5000跳/秒,跳频带宽达2.56MHz,数据传输速率最高可达19.2Kb/s,对杂散、相位噪声等指标要求高,因此,系统对频率合成器相应提出较高的要求。本文设计的频率合成器的指标要求如下:

· 频率范围:1.6MHz~80MHz

· 频率转换" title="频率转换">频率转换时间≤10μs

· 频率间隔:10Hz

· 相位噪声:≤-100dBc/Hz@1kHz

· 杂散抑制:≤-60dB

从上述指标可以看出本频率合成器具有频率覆盖范围相对较宽、频率转换速度快、频谱纯度高的特点,因此设计上具有较高的难度。

2 频率合成方案

为了满足快速频率转换的要求,设计采用了DDS+DSP频率合成方案。通过设计良好的频率基准源和窄带跟踪式滤波器,提高频谱纯度,以达到差分跳频系统对频率合成器的要求。频率合成器的设计框图如图2所示。DDS选用ADI公司生产的高性能AD9951芯片,DSP选用TI公司的TMS320C6418。

2.1 AD9951波形发生单元

AD9951是ADI公司生产的高度集成化芯片,采用了先进的DDS技术,结合内部高速、高性能D/A转换器,形成可编程、可灵活使用的频率合成功能。AD9951的主要特点如下:400MHz内部时钟;集成化14位D/A输出;32位频率转换字;良好的动态性能,在160MHz输出时,具有大于80dB的SFDR;4~20倍可编程参考时钟倍乘器;串行I/O控制;工作电压1.8V,最大功耗仅为200mW。在设计时时钟频率" title="时钟频率">时钟频率选择为400MHz,则频率分辨率fmin=FTW/2n=400×106/232≈0.09Hz,因此满足步进为10Hz的指标要求。

AD9951采用二线控制方式,将片选CSB低电平有效,数据线采用双向SDIO,数据在时钟SCLK上升沿写入,首先存于输入缓冲器中,采用外部频率更新方式,频率更新信号FUD的上升沿有效。频率合成器加电第一次送数时,所有寄存器送相应数,以后改变频率时只送频率字寄存器04h,控制时序如图3所示。可见要传达32位的频率控制字需要传输8位指令信息和32位数据信息,需要40个时钟周期。

控制芯片选择TI公司生产的TMS320C6418。该芯片是32位的定点DSP,芯片内部集成了1.5Mbit的片内SRAM,具有丰富的外部接口;它使用了超长指令字结构(VLIW)体系结构,一个时钟周期可同时处理8条相互独立的指令,再加上流水线技术,大大提高了并行处理能力和运算能力。TMS320C6418参考时钟为50MHz,内部工作时钟经倍频后达400MHz。通过SPI总线控制对AD9951进行控制,采用20MHz的时钟传输频率,2μs即可完成频率控制字的更新。

2.2 AD9951时钟电路设计

DDS输出信号的质量取决于工作时钟信号的频谱质量,DDS输出信号的最高频率受到时钟频率的限制(最高输出频率小于时钟频率的40%),并且DDS输出信号频率越接近上限,性能指标越差。从提高频率合成器的性能指标来讲,应选择400MHz低相位噪声的时钟做AD9951的频率源,但市场上这种频率源不但价格昂贵,而且性能指标达不到要求。因此,在设计时选用了目前性能优良、时钟频率不太高的晶体作为参考频率的基准源,采用低相位噪声的鉴相器和窄带压控振荡器作为锁相环,用于产生1600MHz的时钟频率。由于只作为点频,因此在环路滤波器的参数选择上主要考虑如何使输出信号频谱特性最优。最后由分频器进行4分频或5分频,即输出400MHz或320MHz时钟信号,设计匹配网络将信号转换为差分输入,供AD9951作为时钟频率,能够有效减少共模干扰。由于DDS杂散分布具有一定的规律性,通过不同的参考时钟将这种规律性破坏,能够有效抑制某些频段的杂散电平信号。

2.3 滤波器设计

由于DDS采用数字化技术,最终合成信号是经D/A转换后得到的,其频谱含有丰富的高次频谱分量,必须将它们滤除,才能得到频谱纯净的正弦波输出,因此对滤波器的要求很高。在设计滤波器时,由于发射信号为短波波段的1.6MHz~30MHz,频率较低,因此频谱质量较好,在设计时只采用了七阶椭圆滤波器,截止频率为80MHz,后端通过隔离放大后输出。收频率输出信号进行了上变频,其频率为50MHz,因此实际输出频率达51.6MHz~80MHz,频率相对较高,因此在七阶椭圆滤波器的后端再接一个数字式跳频调谐滤波器,该滤波器由数量较多的二进制电容、电感组成,通过电子开关连接所需电容、电感构成滤波网络,通过DSP对其进行控制。调谐频率与输出频率保持一致,过滤带非常窄,因此能够达到比较理想的滤波效果。收、发频率通过七阶椭圆滤波后端的电子开关进行选择,并由DSP进行控制。收发进行隔离,防止信号相互干扰。

3 电磁兼容性设计

由于该频率合成器是用于快速跳频系统,电台的数据传输速度最高可达19.2Kb/s,对杂散和噪声的抑制要求高,由于是高速数模混合电路,所以在设计时应对电磁兼容性进行充分考虑。PCB板设计为4层板。其中第2层为地平面,并将地平面在AD9951芯片下面分为数字地和模拟地。第3层为电源平面,分成AVDD、DVDD、1.8 V、3.3 V四部分,分别为AD9951的模拟部分、数字部分电路供电。其余外围电路的电源单独通过稳压块提供。同时使用滤波器组件对全部频段进行电源滤波。PCB板的1、4、2层走信号线,走线尽可能短,防止在信号线上出现不必要的过孔以免损害信号电气特性完整性。信号线间距D与线宽W之间满足D≥3W以避免信号窜扰。按照传输线理论设计好带线和微带线,避免信号线连接处阻抗不匹配,防止反射。为了减少时钟泄漏对其他信号的干扰,在屏蔽盒内做出一个腔体把时钟源与系统的其他部分进行隔离。在PCB布线时,尽量让时钟线远离其他信号,同时在时钟线的两边加地线屏蔽。

4 测试结果

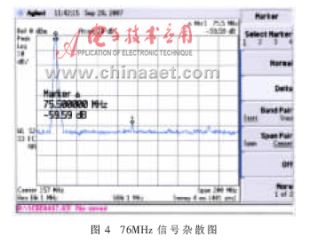

通过图4、图5可以看出,该频率合成器在76MHz处的杂散抑制和相位噪声分别达到了-65dB和-113dBc/Hz@1KHz,谐波分量达到-59.6dB,完全满足指标要求。频率转换时间通过采用安捷伦公司生产5372A调制域分析仪进行测量,实际频率转换时间仅为2μs。

在基于AD9951的差分快速跳频系统频率合成器的研制过程中,为了降低相位噪声、提高杂散抑制度和频率转换速度,在电磁兼容、电路布局以及PCB设计等方面进行了精心的考虑,达到了较为理想的性能指标。

参考文献

[1] 费元春,苏广川,米红,等.宽带雷达信号产生技术.北京:国防工业出版社,2002.

[2] 谢仁宏,是湘全.基于DDS的低相噪频率综合源设计.现代雷达,2003,25(12):41-43.

[3] 夏永祥,郭德淳,余军,等.基于AD9858的快速捷变频频率合成器的设计.现代雷达,2005,27(7).

[4] 李明,戚仁华,朱红琛.短波宽带快速跳频通信技术研究.通信技术,2000,110(3).