引言

长条的LED显示屏在生活中应用得很多,这种显示屏的控制电路简单,扫描线有限,显示信息量也不是很大。当显示信息量比较大时,若采用一般的长屏显示屏,显示信息过慢,即使采用超长屏的显示屏,其数据输出速率也很低,而且显示屏的刷新频率也不一定能满足显示需求。矩形显示屏显示的信息量大,并且可以按需要扩展显示屏的高度,不存在频率上的限制,能够弥补长条显示屏显示信息时存在的不足。本设计使用双RAM技术来组织用于控制矩形显示屏的控制系统数据,提高了信息垂直循环显示时的存储器效率,大幅度降低了对数据存储器的占用率,并且对刷新频率的要求也不是很高。

1 显示数据组织

需要显示的区域小于或等于实际显示区域时,采用静态显示即可。但大多时候需要显示的区域大于或等于实际显示区域,如图1所示。为了简化问题的分析,本文将显示区域高度设置为LED显示屏高度的4倍,宽度等于LED显示屏宽度。设显示屏的高度为Lh,宽度为Lw,则显示区域高度Dh=4Lh,宽度Dw=Lw。本文以单色显示作为描述对象,且Bw=Bn=8(Bw为扫描线条数,Bn为输出数据宽度),如图1所示。

对于一个LED显示屏,宽度Lw和高度Lh确定后,显示屏单元板的排列方式也就确定了。单元板相邻的两条扫描线之间的距离为Sw,显示屏有Bw条扫描线,分别是Y0,Y1,…,YBw-1。每Sw行对应一位显示数据,显示屏上的每一个点对应于存储器中某个字节的某一位。Bw条扫描线分别指向:Y0=O,Y1=Sw,…,BBw-1=(Bw-1)Sw。用静态显示数据组织方法分别对显示块A、B、C、D组织显示数据。首先对显示块A的显示信息进行组织(X为列号):

①X=0,即当前扫描线各行与第O列相交各点的显示数据按D0,D1,…,DBw-1的顺序存储在存储器的第一个存储单元中。

②X值增加1,当前扫描线各行与X值对应列相交各点的显示数据存储在存储器的下一个存储单元中。直至将X=O至X=Dw-1的Dw个数据按顺序全部存储在存储器中。

③Bw条扫描线向下移动一行,重复第①至②步,直到Y0移动到Sw-1行时。

④数据组织结束。

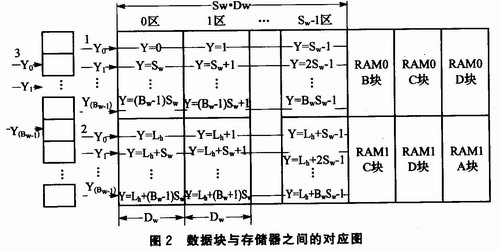

显示区域B、C、D分别按照A的数据组织方式去组织显示数据。组织后的显示数据块按A、B、C、D的顺序存储在RAM0里,然后将RAM0中的显示数据块A、B、C、D按B、C、D、A的顺序拷贝到RAMl中,任何两个相邻显示块的显示数据在两块RAM中都有相同的地址存储区域。RAM0和RAMl的显示数据与存储器的对应关系如图2所示。

如图2所示,扫描组1从Y0=0到Y0=Sw-1,对应显示块A,数据已组织存放在存储器中,可以直接输出显示数据;扫描组2从Y0=Lh到Y0=Lh+ Sw-1,对应显示块B也已经组织好,可以直接输出。但是扫描组3,它的位置非同一般,它的扫描线分别对应着两个块A和B;第O,1,…Bw-1条扫描线分别对应显示块A扫描组1的1,2,…,Bw-2;而第Bw-1条扫描线就对应显示块B扫描组2的第O条扫描线。如果要在显示屏上显示扫描组3对应的这一屏数据,就一定要同时使用到扫描组1的第1,2,…,Bw-1条扫描线和扫描组2的第O条扫描线组织的显示数据作为输出数据。由于显示块A和B的显示数据是分别组织的,这时就要取RAM0的D0,D2,…,DBw-1和RAMl的D0位作为输出到显示屏的Bw位数据,这就需要在两块RAM同时输出的2Bw位中选择需要的Bw位作为输出数据,并且这Bw位数据是连续的。

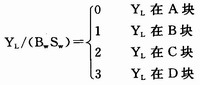

显示步骤(在此只考虑垂直移动显示效果);双RAM技术将显示数据输出的时候,是将两块RAM中相同地址的两个数据同时输出。所以,如果设置RAMO为主存储器,RAMl为从存储器,则将两块RAM的显示数据存在一块串行存储器中时,偶地址单元应存储RAM0的数据,奇地址单元存储RAMl的数据,由于数据宽度为8,所以每次输出16位数据。如果显示区域中以(XL,YL)点为显示起始点,在LED屏上显示一屏显示信息,则其数据选择控制位只与YL、扫描线和扫描宽度Sw有关。显示区域的起始行坐标为YL,一块显示区域有Bw·Sw行,则YL所在的块为:

这里讨论YL在实际显示区域的坐标没有多大意义,只须注意YL在当前显示块的相对坐标,NL=YL%(Bw·Sw)就是YL在当前显示块的相对纵坐标,则相对坐标为(NL,YL)。动态显示的基础是静态显示,静态显示以从特定行显示一屏为特征,当显示屏从第YL行开始显示信息时,因为一块显示区域有Sw·Dw个数据,则YL所在块显示数据的起始地址为:

![]()

一块显示区域分为Sw个区,则YL所在的分区记作:

![]()

一区存放有Dw个显示数据,所以YL所在分区地址与所在块起始地址之间的相对偏移地址为(YL%Sw)·Dw。所以,只要知道了显示信息的起始行坐标,就能得到显示数据在存储器中的存储地址。

NL=YL/(Bw·Sw),这里记i=NL/Sw(0≤i≤7),表示显示信息跨越两个数据块时需要选择的数据位数。存储器输出16位数据[D0,D1,…,D15]后,从Di位控制选择连续的8位数据[Di,Di+1,…,D7,…,D7+i]输出到显示屏。当数据从一个字节的Di位开始输出16位时,如[Di,Di+1,…,D7,…,D15,D0,…,Di-1],前面8位在当前显示是多余的几位数据,后面8位数据[D8+i,…,D15,D0,…,Di-1]正好是要输出到显示屏的8位数据。当这16位数据串行输出到一个8位的移位寄存器中时,移位寄存器刚好可以容纳高8位数据,并将其输出显示。之后各列数据的输出情况同样如此,不需要额外的指令或电路来对输出数据进行选择输出。只是在每行第一列数据输出前,通过单片机模拟i个时钟脉冲输出到存储器,让输出数据产生错位,使数据从Di位开始输出。另外,当显示信息刚好是A、B、C、D块中的某一块时,无须产生模拟脉冲对数据进行选择,而是直接将数据输出显示。通过分析可知,SPI模块刚好具有这个功能,通过单片机额外模拟i个时钟脉冲,输出到串行存储器的时钟信号端,可以使数据错位,从指定的某一位Di开始输出。当显示信息跨越Sw-1区间时,如果一场显示还没有完毕,内存地址应返回到YL所在块的起始地址,并从起始地址开始输出显示数据,单片机模拟的脉冲数i也相应发生变化。

2 LED显示屏控制系统设计

LED显示屏控制电路。为了提高数据输出效率,采用Ramtron公司的带SPI功能模块的VRS51L3074单片机。VRS51L3074的时钟频率为40 M-Hz,指令周期短,处理速度快,效率高;工作电压在3.3 V左右,但是可以兼容5 V。SST25VF016B是一款具有SPI接口的8引脚串行Flash。7 4LSl64为移位寄存器。

2.1 VRS51L3074的SPI功能模块

VRS51L3074的SPI时钟频率可以在SysClk/2~SysClk/1024范围内调整,SPI时钟频率最高可以达到20MHz。当VRS51L3074作为SPI主机时,可以对SPI运行控制、配置和状态监控以及其他的一些工作环境进行设置。

配置寄存器SPICONFIG:主要对片选信号控制模式、SPI中断进行设置。

状态寄存器SPISTATUS:主要用于对SPI运行状态的监控。

传输字长寄存器SPISIZE:设置传输字长,本文设置为16位,即每次输出16位数据。

控制寄存器SPICTRL:对SPI时钟速率、时钟相位/极性、片选信号,以及SPI时钟频率进行设置。

数据寄存器SPIRXTX0~SPIRXTX3:用于对SPI接口32位收发缓冲器的访问,对数据寄存器执行写操作是将数据送入发送缓冲器中,对数据寄存器执行读操作是从接收缓冲器中取出收到的数据。SPI接口的发送和接收缓冲器都采用双缓冲结构,从硬件上减少数据冲突并提高数据传输效率。在主模式下对SPIRXTX0寄存器执行写入操作将启动SPI传输。当传输字各行长大于8时,应最后向SPIRXTX0寄存器写入。

向串行Flash输入控制信号和数据地址后,启动串行Flash传输数据,在SPI时钟驱动下输出显示数据,并且可以用单片机模拟串行Flash时钟信号控制任意位数据输出。

2.2 数据选择控制电路

LED显示屏控制系统如图3所示,VRS51L3074单片机内部自带精确的40 MHz振荡器,不需要外部晶振电路提供系统时钟。数据显示采用内存为16 Mb的SST25VF016B。双RAM技术输出显示数据的时候,是将两块RAM中相同地址的两个数据同时输出,所以,将两块RAM的显示数据存放在一块串行存储器中时,偶地址单元应存储RAM0的数据,奇地址单元存储RAMl的数据,数据输出时每次输出16位数据。串行存储器和单片机的工作电压都在3.3 V左右,但是VRS51L3074可以兼容5V,简化了控制电路。控制信号和显示数据在输出到寄存器74LS164和显示屏的时候,需要用74LVC07进行电平转换。

控制系统控制显示数据输出的流程为:

①将扫描线行地址通过P2端口的低4位送给LED显示屏。

②通过显示数据在显示区域中的位置,计算显示数据在存储器中的地址,并计算出数据选择的位数i。

③通过单片机P3.0口模拟移位脉冲,输出到串行Flash时钟信号,移位脉冲数由数据选择位数i决定。使输出数据产生错位,正确地选择输出显示数据。

④启动SPI读取显示数据,SPI传输字长设置为16位。模拟脉冲已经输出到串行Flash使数据产生了错位,输出16位数据[Di,Di+1,…,D7,…,D15,D0,…,Di-1],输出到显示屏的数据[D8+i,…,D15,D0,…,Di-1]在高8位,经过移位刚好可以存放在移位寄存器中。每行第一个数据输出后,此行各列数据都直接输出。

⑤16位数据输出完毕后,通过P3.1脚产生一个SCK脉冲,将移位寄存器74LSl64中的数据输出移入到单元板的串行移位寄存器74HC595中。

⑥重复第④至⑤步,直到一行数据全部输出完毕后,由P3.2产生一个RCK脉冲,读取的一行数据将输出显示,然后扫描线下移一行。

⑦重复第①至⑥步。

此电路有这样几个特点:显示数据从串行Flash输出后,不经单片机的处理,直接以DMA方式输出到移位寄存器74LSl64,同时实现串并转换,既节省数据处理时间,又提高显示效率。在每场数据输出之前,通过信息在显示区域中的地址计算数据选择位数i,并通过P3.O端口模拟i个脉冲输出到串行Flash,移出i位数据,数据产生错位,使输出显示的数据在16位输出数据的高8位,可以直接存放在移位寄存器中,输出到显示屏。以后同行各列的显示数据输出时,无需再进行数据选择位的判断,直接将显示数据从存储器中输出到显示屏。

存储器效率分析如表1所列。

由表1可知,采用双RAM技术输出显示大大提高了存储器效率,降低了显示数据存储器的占用。当显示信息量较大时,动态数据组织使用的存储器比较多、利用率低,而采用双RAM技术正好解决了这个问题。一块RAM(静态显示时)的存储器效率是100%,双RAM的效率是50%。当有N块RAM时,效率为(N-1)/N。

针对图3所示控制电路,按照数据输出控制流程编写了程序代码。随机显示一屏信息,显示数据已按顺序存储在串行Flash中。

结语

本控制系统利用串行Flash输出数据时的特点,大大地减少了数据处理的时间,将显示数据以DMA方式输出到显示屏,不但提高了显示效率,而且弥补了长条显示屏在显示信息上的不足。双RAM技术大大提高了垂直移动时的存储器使用效率,所有的数据块都是按静态显示方式组织数据,所以每一块RAM的显示数据效率都是100%,双RAM的效率为50%。本文将显示数据存放在一块Flash中,效率也为50%,相比动态显示组织方式,降低了垂直移动时显示数据存储器的占用率,提高了存储效率。此外,还可以双RAM技术为基础,扩展出多RAM方式,提高显示的高度,增加每屏显示信息,进一步提高存储效率。本系统仍有改进的空间,譬如以双RAM组织显示数据后直接用两个RAM来存放不同的数据,控制显示数据直接输出,以提高输出速率。