ALTERA FPGA在微处理器系统中的在应用配置

2008-11-03

作者:温淑鸿 崔慧娟

摘 要: ALTERA公司SRAM工艺可编程器件应用广泛,专用配置器件比较昂贵。在具有微处理器的系统中,使用微处理器系统的存储器来存储配置数据,并通过微处理器配置FPGA,这种方法几乎不增加成本。微处理器根据不同的程序应用,采用不同的配置数据对FPGA进行配置,使FPGA实现与该应用有关的特定功能。详细介绍了微处理器系统中连接简单的被动串行" title="被动串行">被动串行配置方法和被动并行异步" title="被动并行异步">被动并行异步配置方法。

关键词: 在应用配置 FPGA配置 被动串行 被动并行异步

可编程逻辑器件(PLD)广泛应用在各种电路设计中。基于查找表技术、SRAM工艺的大规模PLD/FPGA,密度高且触发器多,适用于复杂的时序逻辑,如数字信号处理和各种算法的设计。这类器件使用SRAM单元保存配置数据。配置数据决定了PLD内部互连和功能,改变配置数据,也就改变了器件的逻辑功能。SRAM编程时间短,为系统动态改变PLD的逻辑功能创造了条件。但由于SRAM的数据是易失的,配置数据必须保存在PLD器件以外的非易失存储器内,才能实现在线可重配置(ICR)。

1 在应用配置(动态配置)

同一设备在实现不同的应用时,要求FPGA实现不同的功能。如手持多媒体设备,可拍摄分辨率较高的静止图像照,采用JPEG2000压缩,也可传送活动图像,采用H.263,H.264/AVC等。单纯使用软件实现速度慢,需要对算法进行精细的优化;而使用硬件实现则速度快,但灵活性差。为此,采用微处理器和FPGA相结合来实现手持多媒体终端,微处理器实现程序控制,FPGA实现大量的规则运算。此外,手持设备的某些应用(如静止图像和活动视频压缩)可能并不同时实现。若在一片FPGA同时实现这些功能,不仅布线复杂,功能难以实现,而且需要更大规模的FPGA。若使用不同的配置数据进行配置,使FPGA在不同时刻实现不同的功能,则FPGA的容量可以显著降低,从而降低设备的体积、功耗及成本。

使用在应用配置时,首先把应用分集,可能同时运行的应用分成一组,耗时的规则运算由FPGA实现,其它由微处理器实现。把一个FPGA芯片的多个配置文件连续地存放在系统存储器中,在程序执行时,微处理器把对应特定应用的配置数据装载到FPGA中并完成初始化,在FPGA进入用户模式后就能实现特定的功能了。这种方法可以采用更小规模的FPGA,不必使用专用的昂贵配置芯片(如ALTERA的EPC1、EPC2等)来存储配置数据,因而可显著地节省系统成本。

ALTERA SRAM工艺的FPGA配置方式" title="配置方式">配置方式主要分为两大类:主动配置和被动配置。主动配置方式由PLD器件引导配置操作过程,它控制着外部存储器和初始化过程;而被动配置方式则由外部计算机或控制器控制配置过程。根据数据线的多少又可以将PLD器件配置方式分为并行配置和串行配置两大类。下面以ALTERA APEX20KC 系列器件为例,介绍两种在微处理器系统里连接简单且使用方便的配置方式:被动串行配置和被动并行异步配置。

2 被动串行配置(PS)

被动串行配置的主要配置引脚如下:

nSTATUS:双向漏极开路;命令状态下为器件的状态输出。加电后,FPGA立即驱动该引脚到低电位,然后在5μs内释放它。nSTATUS经过10kΩ电阻上拉到Vcc,如果配置中发生错误,FPGA将其拉低。在配置或者初始化时,若配置电路将nSTATUS拉低,FPGA 进入错误状态。

nCONFIG:配置控制输入。低电位使器件复位,由低到高的电位跳变启动配置。

CONF_DONE:双向漏极开路;在配置前和配置期间为状态输出,FPGA将其驱动为低。所有配置数据无错误接收并且初始化时钟周期开始后,FPGA将其置为三态,由于有上拉电阻,所以将其变为高电平" title="高电平">高电平,表示配置成功。在配置结束且初始化开始时,CONF_DONE为状态输入:若配置电路驱动该管脚到低,则推迟初始化工作;输入高电位则引导器件执行初始化过程并进入用户状态。

DCLK:时钟输入,为外部数据源提供时钟。

nCE:FPGA器件使能输入。nCE为低时,使能配置过程。单片配置时,nCE必须始终为低。

nCEO:输出(专用于多片器件)。FPGA配置完成后,输出为低。在多片级联配置时,驱动下一片的nCE端。

DATA0:数据输入,在DATA0引脚上的一位配置数据。

PORSEL:专用输入,用来设置上电复位(POR)的延时时间。

nIO_PULLUP:输入。低电平时,在配置前和配置期间使能内部弱的上拉电阻,将用户管脚拉至VCCIO。

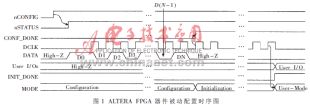

几乎所有ALTERA FPGA器件都支持被动串行配置。被动串行配置的时序图如图1所示,在这种配置方式中没有握手信号,配置时钟的工作频率必须在器件允许的范围,最低频率没有限制。为了开始配置,配置管脚和JTAG管脚所在的bank的VCCINT、VCCIO必需供电。FPGA上电后进入复位状态。nCONFIG被置为低电平,使FPGA进入复位状态;nCONFIG由低到高的电位跳变启动配置过程。整个配置包括三个阶段:复位、配置和初始化。当nSTATUS或者nCONFIG 为低电平时,器件处于复位状态。当nCONFIG由低变高时,器件脱离复位状态,并且释放漏极开路的nSTATUS管脚。在nSTATUS释放后,被外部电阻拉高" title="拉高">拉高,这时nSTATUS和nCONFIG同时为高电平,FPGA准备接收配置数据,配置阶段开始。在串行配置过程中, FPGA在DCLK上升沿锁存DATA0引脚上的数据。成功接收到所有数据后,释放CONF_DONE引脚,并被外部电阻拉高。CONF_DONE由低到高的转变标志配置结束,初始化开始。此后,DCLK必须提供几个周期的时钟(具体周期数与DCLK的频率有关),确保目标芯片被正确初始化。初始化完成后,FPGA进入用户工作模式。如果使用了可选的INIT_DONE信号,在初始化结束后,INIT_DONE被释放,且被外部电阻拉高,这时进入用户模式。DCLK、DATA、DATA0 配置后不能三态,可置高或者置低。

在配置过程中,一旦出现错误,FPGA将nSTATUS拉低。系统可以实时监测,当识别到这个信号后,重新启动配置过程。nCONFIG 由高变低,再变高可以重新进行配置。一旦nCONFIG被置低,nSTATUS 和CONF_DONE 也将被FPGA置低。当nSTATUS和 nCONFIG同时为高电平时,配置开始。

图2是采用微处理器的FPGA被动串行配置方案的简化电路图。配置过程为:由微处理器将 nCONFIG 置低再置高来初始化配置;检测到nSTATUS变高后,就将配置数据和移位时钟分别送到DATA0和DCLK管脚;送完配置数据后,检测 CONF_DONE 是否变高,若未变高,说明配置失败,应该重新启动配置过程。在检测 CONF_DONE 变高后,根据器件的定时参数再送一定数量的时钟到DCLK管脚;待FPGA初始化完毕后进入用户模式。如果单片机具有同步串口,DATA0、DCLK使用同步串口的串行数据输出和时钟输出,这时只需要简单把数据字节或字锁存到发送缓冲器就可以了。在使用普通I/O线输出数据时,每输出1个比特,就要将DCLK置低再置高产生一个上升沿。它比ALTERA 公司手册给出的电路连接图更有效地使用了存储器。

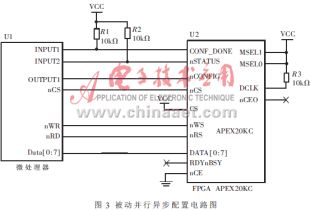

3 被动并行异步配置

如同被动串行配置一样,被动并行异步配置也包括三个阶段:复位、配置和初始化。被动并行异步配置电路图如图3所示。当nSTATUS或者 nCONFIG 为低电平时,器件处于复位状态。微处理器在nCONFIG 管脚产生一个由低到高的跳变启动FPGA的配置。当nCONFIG变高后,器件脱离复位状态,并且释放漏极开路的nSTATUS管脚,FPGA准备接收配置数据,配置阶段开始。在配置阶段,微处理器把FPGA当作存储器,进行写操作,即微处理器先使片选有效,然后把8比特数据送到Data[0:7]管脚上,再把nWS拉低。在nWS的上升沿,FPGA锁存配置数据,并驱动管脚RDYnBSY 到低电平,表示 FPGA正忙于处理配置数据,微处理器可执行其它功能。在RDYnBSY低电平期间,FPGA使用内部振荡器时钟处理配置数据。当FPGA准备接收下一字节的配置数据时,它驱动RDYnBSY到高电平。微处理器检测到这一高电平,便送下一字节数据到配置管脚。为了节省一根用来检测RDYnBSY 的I/O线,可采用读存储器的方法读FPGA,其中nRS为存储器读信号,在 nRS 有效期间,RDYnBSY 信号被送到数据线D7上。也可以不检测RDYnBSY,也不读FPGA,简单地等待延时 tBUSY(max)+tRDY2WS+tW2SB之后就写下一个配置数据字节。FPGA每处理一字节配置数据后,若发现错误就会将nSTATUS 拉低,暗示配置出错。微处理器可以检测这一错误,并重新进行配置。如同被 动串行配置一样,FPGA在正确接收到所有配置数据后,将释放CONF_DONE信号,于是该管脚被外部上拉电阻拉高,表示配置结束,初始化开始。

4 配置数据文件的生成

Altera的MAX+PLUS II或Quartus II开发工具可以生成多种格式的配置文件,用于不同配置方法。不同目标器件,配置数据的大小不同。配置文件的大小一般由二进制文件(扩展名为.rbf)决定。Altera提供的软件工具不自动生成.rbf文件,需要按照下面的步骤生成:① 在MAX+PLUS II编译状态,选择文件菜单中的变换SRAM目标文件命令; ② 在变换SRAM目标文件对话框,指定要转换的文件并且选择输出文件格式为 .rbf(Sequential),然后予以确定。

本文介绍了廉价的ALTERA FPGA器件配置方法,并讨论了其应用配置在手持设备上的应用。

参考文献

1 Configuration Handbook.Volume 1 & volume 2. CF5V1-1.0. ALTERA, 2003(9)

2 王玉花,郭书军,葛纫秋.FPGA器件的在线配置方法.单片机与嵌入式系统应用,2004(3)

3 唐晓泉,黄益庄.基于SRAM的可重配置电路.电子产品世界,2001(1):58~59

4刘晓明,王 军,谢明钦. 基于单片机的复杂可编程逻辑器件快速配置方法. 电子技术应用,2002;28(10):9~11