挑战EUV光刻?NIL靠谱吗!

2021-10-28

来源:半导体行业观察

芯片制造离不开光刻机,且制程越先进,其重要性越凸出,占芯片制造总成本比例也越高,总体来看,光刻机的成本占总设备成本的30%。

当制程发展到7nm后,必须要用到EUV(极紫外线)光刻机,这种光刻机只有ASML能够生产,且产能有限,厂商们要买到,并不容易,且ASML要优先供应台积电、三星、英特尔这三家股东。

难以逾越的EUV

EUV是一种曝光设备,它可以根据发出的光的种类减少工序数量并节省时间和金钱。现有的半导体材料氟化氩具有193nm的光波长。波长越短,可以雕刻出更精细的电路。使用氟化氩,以某种方式可以实现7nm的制程工艺。但在这之下就很难了。由于台积电、三星等主要代工企业已达到5nm及以下的工艺,氟化氩曝光设备面临限制。

EUV设备克服了这一限制。EUV的波长为13.5nm,可以实现5nm以下的工艺。因此,全球生产先进制程(10nm以下)的芯片代工企业都在努力引进 EUV 设备,这使得EUV供给非常紧张。如果有需求,可以通过增加供应来平衡。然而,EUV设备开发难度很大,一年只能生产十几台,ASML今年要生产的EUV设备数量约为40台。这40台被台积电、三星电子和英特尔瓜分。2019年,EUV占ASML销售额的31%,但到2020年,就占到了43%,成为最“赚钱”的产品线。

一台EUV设备的高度可以达到4到5米,重量接近180吨。这样的高科技设备,其中的零部件数量也是巨大的,大约有10万个。EUV设备曝光是在真空室中完成的。还需要以0.005℃为单位精细控制温度的技术。由于光学系统对污染物非常敏感,因此还必须实时进行内部监控。由于这些特点,生产EUV设备并不容易。

EUV 设备的性能取决于镜头和反射镜的分辨率。分辨率通常与镜头像差 (NA) 成正比。出于这个原因,努力增加 NA 是绝对必要的。当NA值高时,分辨率提高,光线变得更清晰,可以实现更精细的半导体电路。正是出于这个原因,ASML 收购了全球光学公司蔡司的股份。

目前,EUV设备NA值为0.33。ASML 计划通过研发将下一代 EUV 设备的 NA 提高到 0.55。这称为高NA。高 NA 可最大限度地减少光失真并允许更精细的电路实现。ASML 计划在 2023 年推出基于高数值孔径的 EUV 设备原型。下一代EUV设备的开发有望进一步巩固其在微纳制程半导体曝光设备市场的垄断地位。

随着半导体制造商将基础设施转向EUV设备,需求猛增,但供应却跟不上。即使有生产目标,不能按时交货也是很常见的。即便是现在,如果要采购ASML EUV设备,也要等上一年多。

通常,一台EUV 设备的价格在1亿至2亿美元之间。虽然非常贵,但半导体厂商即使付出更多,也想尽快拿到EUV设备。

NIL比拼EUV

由于EUV设备太过昂贵,且生产难度很高,近些年,业界一直在寻找其它办法,不用EUV光刻机,能不能生产7nm及以下的芯片?事实上,也有厂商是这么想并打算这么干的,因为通过DUV光刻机进行多重曝光,理论上也能达到7nm。但这种办法非常复杂,对技术要求非常高,同时良率低,晶圆的损耗比较大,所以如果能够买到EUV光刻机,就不可能用这种办法,这种办法生产出来的芯片,完全没有市场竞争力。

纳米压印光刻 (NIL)、定向自组装 (DSA) 和等离子激光等技术被认为是EUV的替代品。NIL 是一种将纳米图案印章转移到晶圆上的方法,就像它被涂漆一样。它被提出作为一种绘制 32nm 以下电路的方法。它比 EUV 更经济,因为它不使用镜头。佳能等厂商在 EUV 研发如火如荼的时候就开始开发 NIL。

DSA是一种通过将具有不同特性的聚合物合成为单个分子,将其涂覆在晶圆上并加热来获得精细图案的技术。由于不使用掩模,可以减少工艺数量,从而可以降低成本。然而,就所使用的技术而言,它不如 NIL。此外,无掩模等离子激光纳米技术被认为是一种替代方案,因为它具有自由改变电路图案的能力。然而,它仍达不到 EUV的效果。

总体来看,NIL是一个不错的发展方向。

NIL技术比光刻的起步晚,最早追述到上个世纪末,由华裔科学家周郁(Stephen Chou)教授在1995年首次提出纳米压印概念。该技术将微电子加工工艺融合于印刷技术中,解决了光学曝光技术中光衍射现象造成的分辨率极限问题,因此理论上具备比光刻更高的分辨率,可生产出电路线宽更窄的器件。除此之外,高效率、低成本、适合工业化生产等优势,也使得NIL一直受到业界的重视,被称为是微纳加工领域中第三代最有前景的光刻技术之一。

NIL 基于机械复制,不受光学衍射的限制。它可以潜在地实现低于 5nm 的分辨率,并且以非常低的成本实现非常好的关键缺陷 (CD) 控制。由于其优异的性能,NIL 可以满足广泛的半导体应用。它可以大幅度降低光刻成本,可与EUV一战。

图:EUV与NIL的对比(来源:DIGITIMES)

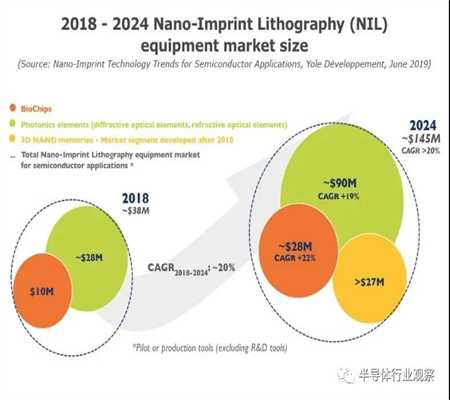

据Yole统计,NIL设备复合年增长率将超过 20%,到 2024 年生产的年收入将达到约 1.45 亿美元。目前,NIL主要用于增强现实、3D传感和数据通信/电信中需要严格和复杂模式的光学光子元件。同时,NIL工艺也引起了存储器厂商的兴趣,特别是20nm以下先进制程,目前的光刻方案成本太高。因此,对于下一代 3D NAND 存储器,NIL是非常有竞争力的成本效益选择。

NIL 供应商在每个特征尺寸范围内都有一个明显的领导者。在纳米范围内,EVG 占主导地位,尤其是在衍射光学元件 (DOE) 中。SUSS MicroTec 在微尺度范围内占据了强大的市场份额。

下面看一下NIL的技术细节。

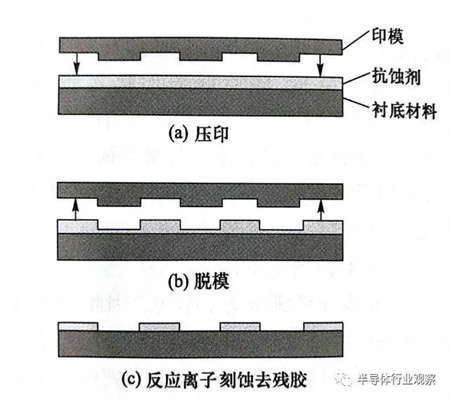

一般情况下,NIL使用电子束刻蚀等手段,在衬底上加工出所需要的结构作为模板。由于电子的衍射极限远小于光子,因此可以达到远高于光刻的分辨率。

NIL制造设备利用图案化技术,涉及现场/逐场/单次沉积和通过喷射技术沉积到基板上的低粘度抗蚀剂的曝光。带图案的掩模下降到流体中,然后通过毛细作用迅速流入掩模中的浮雕图案。在此填充步骤之后,抗蚀剂在紫外线辐射下交联,然后去除掩模,在基板上留下图案化抗蚀剂。

与EUV光刻设备产生的图案相比,NIL以更高的分辨率和更高的均匀性忠实地再现图案。此外,由于这项技术不需要先进光刻设备所需的一系列宽直径镜头和昂贵的光源,NIL 设备实现了更简单、更紧凑的设计,允许将多个单元聚集在一起,以提高生产力。

研究已经证明 NIL 分辨率优于 10nm,使该技术适用于使用单个掩模打印几代关键内存级别。此外,仅在必要时才使用抗蚀剂,从而消除材料浪费。鉴于压印系统中没有复杂的光学器件,当与简单的单级处理和零浪费相结合时,工具成本的降低使其成本模型非常适用于半导体存储器应用。

DRAM 和相变存储器等高级存储器具有挑战性,因为这些设备的路线图要求持续缩放,达到14nm,甚至更先进制程。缩放也会影响覆盖预算。例如,对于 DRAM,某些关键层上的叠加比 NAND 闪存紧密得多,误差预算为最小半间距的 15-20%。对于 14nm,这意味着 2.1nm - 2.8nm。DRAM 器件设计也具有挑战性,并且布局并不总是有利于间距划分方法,例如自对准双图案化 (SADP) 和自对准四重图案化 (SAQP)。这使得直接印刷工艺NIL成为一种很有竞争力的解决方案

NIL的进展

日本存储器大厂铠侠(Kioxia)与佳能,以及光罩/半导体厂商大日本印刷株式会社(DNP),经过了4年的研发,于近期研发出了NIL的量产技术。

目前,铠侠已将其应用到了15nm的NAND闪存制造上,并表示到2025年应该可以应用到5nm的芯片制造上。

铠侠表示,NIL 技术与EUV光刻技术相比,可以大幅度的减少能耗,转化效率高,耗电量可压低至EUV 技术的10%,同时,NIL设备也很便宜,投资可降低至EUV光刻机的40%。

有专业人士指出,NIL技术也许能够推进芯片制程至5nm,但可能更适应于NAND这种3D堆叠的闪存芯片,不一定适用于所有芯片。

合作厂商之一的佳能,则表示要努力将NIL 量产技术广泛应用于制造DRAM 及PC 用的CPU 等逻辑芯片的设备上。