Optimality在多个场景的时域仿真中高效性的深度研究

电子技术应用

黄刚,吴均

深圳市一博科技股份有限公司

摘要: 随着产品的速率及复杂性越来越高,针对仿真而言,除了要求仿真本身具有非常高的精度外,还对仿真的效率提出了很高的要求。具体到不同的信号模块,如DDR系统或者高速串行信号上,基于速率越来越高,越来越希望仿真给能出“最优解”的配置,例如DDR5颗粒的ODT的最优配置,高速信号芯片的加重均衡的最优配置等参数。那么如何在成百上千种组合的参数中选择相对最优的参数呢?传统的软件只能通过大量的扫描来进行筛选,在仿真时间和工程师的精力两方面都有比较大的耗费。使用Optimality软件,通过分享一些具体的仿真案例,展现软件的智能性,帮助使用者更快速挑选出最优的参数,使DDR及高速串行的仿真工作变得更加轻松,充分体现出Optimality软件的高效性。

中图分类号:TN402 文献标志码:A DOI: 10.16157/j.issn.0258-7998.240806

中文引用格式: 黄刚,吴均. Optimality在多个场景的时域仿真中高效性的深度研究[J]. 电子技术应用,2024,50(8):42-47.

英文引用格式: Huang Gang,Wu Jun. In-depth research about the efficient of Optimality in time domain simulation of multiple design cases[J]. Application of Electronic Technique,2024,50(8):42-47.

中文引用格式: 黄刚,吴均. Optimality在多个场景的时域仿真中高效性的深度研究[J]. 电子技术应用,2024,50(8):42-47.

英文引用格式: Huang Gang,Wu Jun. In-depth research about the efficient of Optimality in time domain simulation of multiple design cases[J]. Application of Electronic Technique,2024,50(8):42-47.

In-depth research about the efficient of Optimality in time domain simulation of multiple design cases

Huang Gang,Wu Jun

Shenzhen Edadoc Technology Co.,Ltd.

Abstract: With the increasing speed and complexity of products, for simulation, it not only requirs the simulation itself to have a very high accuracy, but also puts forward high requirements for the efficiency of simulation. Specific to different signal modules, such as DDR systems or high-speed signals, because of the increasing speed, more and more people hope simulation can tell us the "optimal solution", such as the optimal configuration of DDR5 particles ODT, the optimal equalization and de-emphasis configuration of chip. How do you get the relatively optimal parameter among hundreds or thousands of combinations of parameters? Traditional software can only be screened through a large number of scans, which has a relatively large cost in both simulation time and engineer's energy. In this paper, Optimality software is used. By sharing some specific simulation cases, we can see the intelligence of the software, which can help us select the optimal parameters more quickly, make the simulation work of DDR and high-speed module easier, and fully reflect the efficiency of this software.

Key words : Optimality;DDR5;DDR4;ODT;System SI;emphasis and equalization

引言

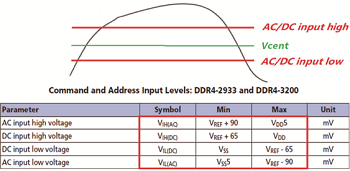

对于业界内两种主要的信号模块:DDR模块和高速串行链路模块,针对信号质量,在仿真评估中都会给出比较明确的时域标准。例如传统DDR4的地址控制信号中,会以高低电平阈值来约束DDR4的信号质量,如图1所示。

图1 DDR4地址控制信号阈值标准

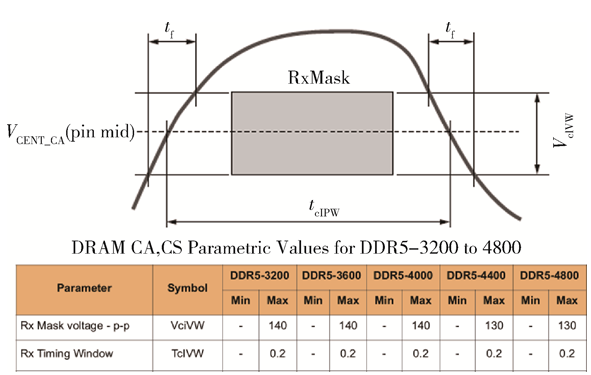

如果从DDR4升级到DDR5,DDR5的地址控制信号质量的判断标准会变成眼图的形式,如图2所示。

图2 DDR5地址控制信号眼图标准

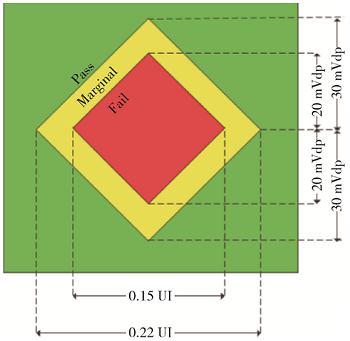

DDR5的眼图判断形式其实就很像传统意义上的高速串行信号了,图3是某芯片的25 Gb/s信号的眼图接收要求。

图3 某芯片25 Gb/s高速串行信号眼图接收标准

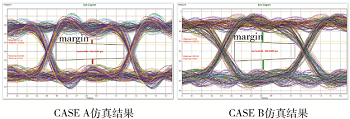

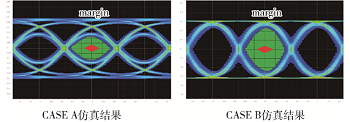

每种不同的信号类型有了对应的判断标准外,不同的工程师在信号质量满足标准后,对裕量的要求可能会不同,图4给出了不同裕量仿真结果对比。大家总是希望有更多的裕量,例如还是上述的DDR4的地址控制信号仿真结果,如图5所示,当两个仿真结果都能满足判断标准之后,相信大家更希望获得case B仿真结果的设计,毕竟它的裕量更大。

图4 DDR4地址控制信号仿真结果裕量对比

图5 25 Gb/s高速串行信号仿真结果裕量对比

同样在高速串行信号也存在同样的选择,眼图裕量大的case总是大家的第一选择。

不同裕量的仿真结果其实代表着仿真参数的不同,在DDR信号仿真中,可能代表着主控芯片驱动或者颗粒ODT值的不同,对于高速串行信号仿真而言,则可能是芯片的加重均衡参数的不同。那么本节就带出一个值得思考的问题,到底在仿真中如何能够准确且快速地找到最佳的参数从而得到最大裕量的仿真结果呢?

本文详细内容请下载:

http://www.chinaaet.com/resource/share/2000006120

作者信息:

黄刚,吴均

(深圳市一博科技股份有限公司, 广东 深圳 518051)

此内容为AET网站原创,未经授权禁止转载。