微型自动切片式三维重构系统的设计[可编程逻辑][工业自动化]

发表于:2015/4/30 下午12:28:00

Apriori算法改进研究及实现[嵌入式技术][数据中心]

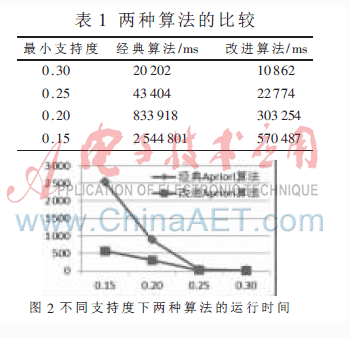

数据挖掘是指从数据库的大量数据中提取出先前未知的、具有潜在实际价值的、隐含的信息[1]。关联规则挖掘就是从海量的数据中寻找数据项间的关联关系。

发表于:2015/4/30 下午12:10:00

一种改进的LLR-SPA译码新算法[通信与网络][信息安全]

针对LDPC码目前广泛使用的译码算法精度低的问题,在LLR-SPA译码算法的基础上提出了一种提高译码精度的新算法。

发表于:2015/4/29 下午10:45:00

数字自动调焦技术在CCD拼接仪中的应用[可编程逻辑][工业自动化]

发表于:2015/4/29 下午5:51:00