文献标识码:A

DOI: 10.19358/j.issn.2096-5133.2018.08.016

中文引用格式:冯传均,何泱,戴文峰.基于FPGA的猝发多脉冲产生系统设计与实现[J].信息技术与网络安全,2018,37(8):70-72.

0 引言

脉冲功率技术是一种功率压缩技术,以较低的输入功率将能量缓慢存储起来,随后在极短时间内释放,以获得极高的峰值输出功率。该技术是应国防科技需要而发展起来的一门新兴科学技术,是获得高电压、大电流等极端电磁参数的重要手段,被广泛应用在科学研究和工业生产等诸多领域中[1-3]。

脉冲功率装置一般由初级能源系统、中间储能系统、脉冲形成系统、开关转换系统和负载系统5个子系统组成。工作时,初级能源系统用于为脉冲功率装置供能,将能量输送至中间储能系统中;中间储能系统常见远重频或猝发脉冲功率装置,通过初步功率压缩为脉冲形成系统供能;脉冲形成系统充电完成后,通过开关转换系统将能量快速传递给负载系统,实现脉冲功率输出。

猝发脉冲是指脉冲功率装置在一次工作周期中输出的多个相同的高功率脉冲,是为了满足特定的工业及科研需求而发展起来的一种脉冲功率技术。要实现猝发脉冲方式工作,脉冲功率装置各个子系统需要按照一定的时序协调工作。为此需要研制一套猝发多脉冲产生系统,控制脉冲功率装置各个子系统按要求工作,同时要实现可调的猝发脉冲参数。

本文采用FPGA控制芯片作为猝发多脉冲产生系统控制中枢,接收上位机控制命令,实现猝发多脉冲信号产生。该系统可输出2路猝发多脉冲信号,猝发脉冲串个数1~5个可调,猝发脉冲串间隔1~200 s可调,猝发脉冲串内部脉冲个数1~5个可调,猝发脉冲串内部脉冲频率1~100 Hz可调,猝发脉冲串内部脉冲宽度等参数可以调节[4-6]。

1 系统总体结构

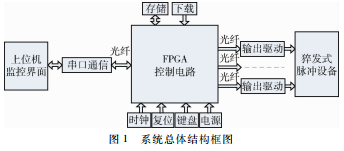

猝发多脉冲产生系统包括:上位机监控界面、串口通信电路、FPGA控制电路、输入/输出隔离电路4个部分。系统总体结构框图如图1所示。其中上位机监控界面基于Visual Basic(VB)软件进行可视化编程实现,通过上位机监控界面可以完成串口通信协议设置、猝发多脉冲信号的参数设置以及系统启动/停止、系统自检等状态控制;上位机和FPGA控制芯片采用RS232串口通信协议,串口通信电路包括:FPGA串口(UART)模块、MAX232芯片和上位机串口三部分,MAX232芯片实现电平转换,解决FPGA的信号电平与RS232的标准不一致的问题;FPGA芯片采用Altera CycloneIV系列,FPGA控制电路包括时钟电路、电源电路、程序下载电路、SDRAM和Flash存储电路、复位电路等;输入/输出隔离电路包括:串口接收信号、串口发送信号和脉冲输出信号,为了增强系统的抗干扰性,FPGA输入/输出信号均采用光纤传输实现。

2 FPGA中控系统程序设计

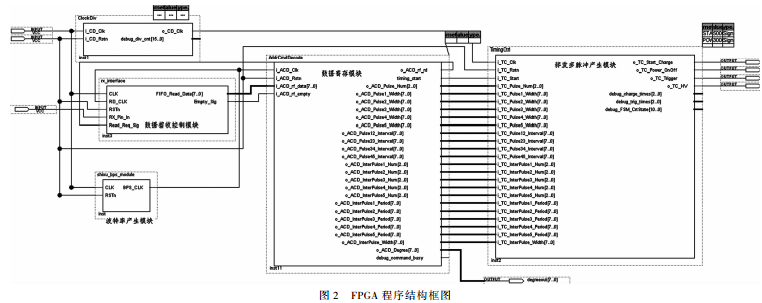

FPGA采用硬件逻辑实现控制功能,具有功耗低、速度快、工作频率高、集成度高等特点,可以完成极其复杂的时序与组合逻辑。本文中FPGA控制电路主要功能有:通过UART模块从串口接收上位机发送的数据,并对接收的数据进行缓存、解析和存储处理,根据控制命令输出2路猝发多脉冲信号。FPGA控制程序采用Verilog HDL硬件描述语言编写,在Quartus II 11.0软件平台开发,核心内容包括:UART数据接收模块、数据寄存模块、猝发多脉冲产生模块三部分。FPGA程序结构框图如图2所示。

2.1 UART数据接收模块

本文设计的UART数据接收模块主要包括波特率产生模块和数据接收控制模块。功能是从串口接收上位机发送的串行数据。

2.1.1 波特率产生模块

在电子通信领域,波特率即调制速度,它是对符号传输速率的一种度量,1 b/s表示每秒传输1个符号。波特率产生模块的功能是产生与RS-232串口通信波特率同步的时钟,其基本思路是对系统输入时钟进行分频得到需要的波特率。本设计中FPGA输入时钟为50 MHz,波特率选择9 600 b/s。

2.1.2 数据接收控制模块

数据接收控制模块主要实现对串行数据的串并转换,转换的串行数据按照既定的数据帧格式进行输出。UART数据接收协议采用1位起始位、8位数据位、1位停止位、无奇偶校验位的格式,在9 600 b/s波特率下,UART数据采集步骤如下:

(1)空闲状态,等待数据起始位0;

(2)根据起始位的标志,判断UART时序起始;

(3)由低到高位串行接收8位数据;

(4)判断结束位1,一帧数据接收完毕。

2.2 数据寄存模块

UART数据接收模块接收的数据经过缓存、解析后,按地址存入相应的数据寄存器中。寄存器作为数据存储的数字设备,2路猝发多脉冲信号参数包括猝发脉冲个数、猝发脉冲间隔、猝发脉冲串脉冲个数、猝发脉冲串脉冲频率、A猝发脉冲串脉宽、B猝发脉冲串脉宽等,共需要21个计数寄存器。

2.3 猝发多脉冲产生模块

猝发多脉冲产生模块根据设置的参数输出猝发脉冲信号,其脉宽以及脉冲个数等参数是通过对数据寄存器保存的数据进行计数来实现的。本文采用有限状态机方式实现猝发多脉冲产生模块的控制。

3 上位机监控界面设计

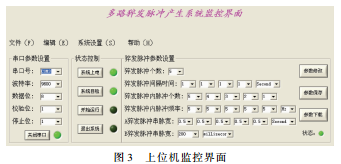

上位机监控界面采用VB软件编程实现,通过调用MSComm串口通信控件设置通信协议,实现与FPGA建立数据通信。操作者通过监控界面预置2路猝发多脉冲信号参数,输入完成后点击参数下载按钮,再点击开始运行按钮后,FPGA开始猝发多脉冲信号的生成。上位机监控界面如图3所示。

4 实验调试

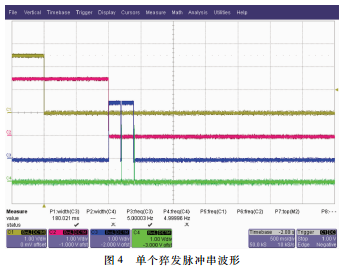

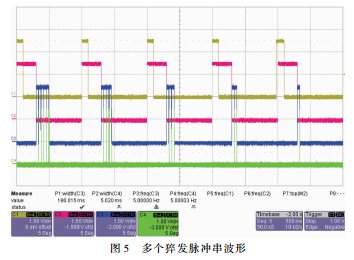

通过上位机监控界面设置串口通信协议,与FPGA控制芯片实现串口数据通信;然后设置猝发多脉冲串的参数,完成后点击数据保存按钮,将数据保存到上位机数据文件;点击数据下载按钮,将设置的数据通过串口发送到FPGA控制芯片;点击开始运行后系统开始猝发脉冲的输出。调试实验中设置猝发脉冲个数为1个,猝发脉冲串内脉冲个数为2个,猝发脉冲串脉冲频率为5 Hz,A猝发脉冲串脉宽为180 ms、B猝发脉冲串脉宽为5 ms,单个猝发多脉冲串波形如图4所示。设置猝发脉冲个数为5个,猝发脉冲串内脉冲个数分别为5、4、3、2、1个,猝发脉冲串脉冲频率为5 Hz,A猝发脉冲串脉宽为180 ms、B猝发脉冲串脉宽为5 ms。多个猝发多脉冲串波形如图5所示。

5 结论

本文所研制的基于FPGA的猝发多脉冲产生系统能够输出2路猝发多脉冲信号,脉冲参数可以调节。该系统利用FPGA内部控制模块实现多路脉冲时序输出和UART接口控制,简化了硬件电路设计;上位机通过VB软件编程的人机交互界面,与FPGA之间采用串口通信,实现远程控制。系统实现远程控制功能,采用模块化设计,可扩展性强。这一设计方案也可以运用到其他时序控制电路中。

参考文献

[1] 刘锡三.高功率脉冲技术[M].北京:国防工业出版社,2005.

[2] 倪晋平,李亚胜,田慧.一种多路时间序列控制仪的设计与实现[J].西安工业大学学报,2012,32(2):88-92.

[3] 罗通顶,郭明安.远程控制高时间分辨率多通道脉冲发生器设计 [J].计算机测量与控制,2015,23(8):2921-2923.

[4] 陈伯俊,周俊敏,马军勇.基于FPGA的高精度多路同步脉冲产生系统研究[J].科学技术与工程,2010,10(19):4794-4796.

[5] 刘纪斌,郭超,罗中省.基于FPGA的多路脉冲同步器设计[J].电子工程师,2008,34(7):3-5.

[6] 王鹏,吕志刚,杜卫东.基于FPGA与ARM的多路时序控制系统设计与实现[J].计算机测量与控制,2012,20(6):1540-1543.

(收稿日期:2018-04-17)

作者简介:

冯传均(1989-),男,本科,主要研究方向:脉冲功率技术应用。