台积电最新SoIC 3D封装蓝图曝光

2026-05-06

来源:芯智讯

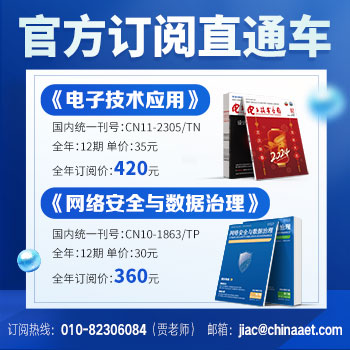

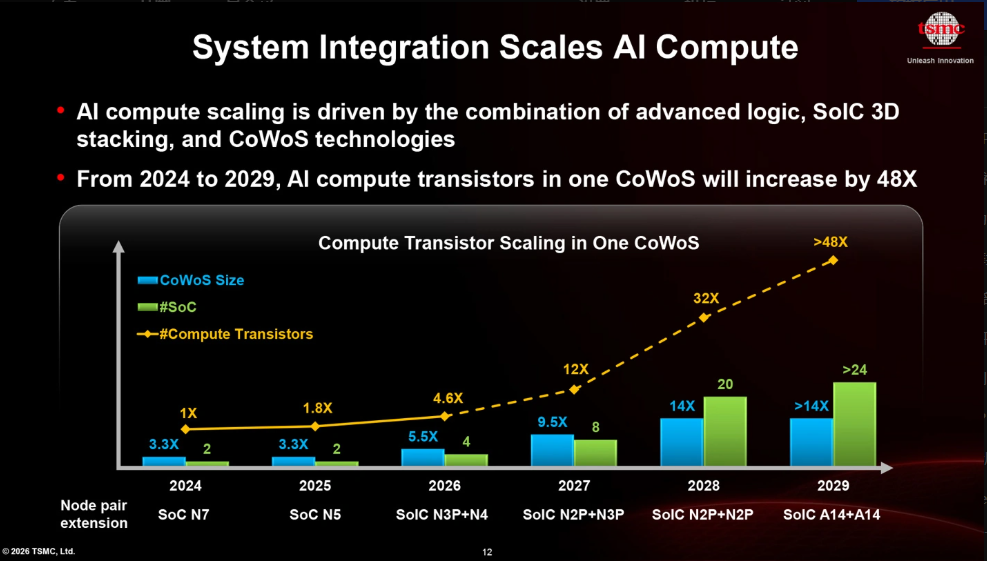

随着人工智能(AI)与高性能计算(HPC) 对芯片性能的要求日益严苛,先进封装技术已成为驱动芯片性能提升的关键。台积电近日在2026年北美技术论坛上公布了最新的SoIC 3D先进封装技术蓝图,宣布将于2029年进一步缩小互连间距,并推出A14对A14制程的SoIC 堆叠技术,展现其在先进封装领域的强大企图心。

根据台积电最新公布的SoIC 3D先进封装技术蓝图,SoIC 的互连间距将从目前的6微米(µm),在2029 年大幅缩小至4.5 微米。这项间距微缩技术对于混合键合芯片堆叠至关重要,因为它直接决定了芯片间能容纳的垂直互连数量。台积电指出,预计2029 年投入量产的A14 对A14的SoIC 技术,其芯片对芯片的I/O 密度将比N2 对N2的SoIC 提升1.8 倍。

SoIC 隶属于台积电3DFabric 先进封装家族,目的在通过超高密度的垂直堆叠技术来缩小芯片体积、提升整体性能,并降低电阻、电感与电容。而此次技术蓝图中的核心变革,是从传统的面对背(face-to-back) 转向面对面(face-to-face) 堆叠。在面对背设计中,信号必须穿越较复杂的路径(包含底层芯片的硅通孔)。而在面对面堆叠中,两颗芯片的主动金属层可以直接对齐,并通过混合铜键合技术连接,大幅缩短了芯片间的传输路径。

根据博通(Broadcom) 的实际测试数据,面对面堆叠的信号密度可达每平方毫米14,000 个信号,远超过面对背堆叠的1,500 个信号。这项跃进带来了更高的带宽与更低的延迟,尽管业界仍需持续克服随之而来的制造与散热挑战。而台积电的高密度芯片堆叠技术已开始进入实战阶段,富士通(Fujitsu) 专为AI 与HPC 工作负载设计的Monaka 处理器,预期将成为首批受益于面对面芯片堆叠技术的系统之一。

另外,博通于2026 年2 月宣布,已开始出货结合2.5D 整合与3D-IC 面对面堆叠技术的3.5D XDSiP 平台,并以此打造2纳米定制化计算SoC供Monaka计划使用,让计算、存储与网络I/O 得以在紧凑的封装中独立扩展。该处理器预计于2027 年问世,届时将可验证高密度的面对面堆叠技术是否已具备商业量产的经济效益。

根据外媒报导,这份SoIC 蓝图呼应了整体半导体产业的趋势转变。随着先进制程微缩变得日益昂贵且困难,晶圆代工厂与芯片设计商正将提升效能的重心转移至先进封装上,包含更大的中介层、更密集的芯片连接、堆叠快取及HBM 整合等。虽然考虑到成本、良率、散热限制及设计复杂度,台积电2029 年的目标并不代表所有先进处理器都会全面采用最高密度的SoIC 方案。但此蓝图明确显示,台积电已将垂直整合视为其先进制程策略中的核心支柱,而非仅仅是利基型的封装选项。